与UP兼容的8位高速ADC-MAX165/MAX166

MAX165/166是8位高速(5µs)ADC,它内部带有采样保持器,转换输出信号与µP兼容。由于内部带有高速采样保持电路,因此它级精确地测量高达50kHz的信号。芯片采用逐次技术(successive apprximaTIon technique)来达到快速转换和降低功耗。它采用单一+5V供电,内部有一个1.23V的能隙基准电压。

MAX165可对单极性信号(singleended)进行转换,MAX166可对差动信号(或叫双极性信号)进行转换,输入电压范围为0~2VREF。

MAX165/166的主要性能参数如下:

●转换时间:µs;

●内部具有采样保持电路;

●精度:MAX165A/166A:±1/2LSB;

MAX165B/166B:±1LSB

●50kHz的信号带宽;

●内部1.23V的基准电压;

●单一+5V供电;

●100ns的数据读取时间;

●15mW的典型功耗

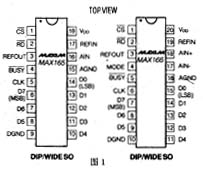

MAX165/166各引脚的作用为:

CS:片选信号,低电平有效。当CS=0时,表示选中该芯片。

RD:读信号,低电平有效。

REFOUT:内部1.23V基准电压输出端。

MODE:MAX166的方式选择端。当MODE=0时,ADC处于异步转换方式MODE=1时,ADC处于同步转换方式或ROM接口方式。

BUSY:忙输出端。A/D转换开始时,BUSY变低;转换结束时,BUSY变为高电平。

CLK:工作时钟引脚。

D7~D0:8条三态数据输出引脚。D7为高位,D0为低位。

DGND:数字地。

AGND:模拟地。

REFIN:基准电压输入端,通常为1.23V。

VDD:电源输入端,通常为+5V。

AIN:模拟输入端。

AIN-:MAX166差动输入的负输入端。

AIN+:MAX166差动输入的正输入端。

2. 工作原理

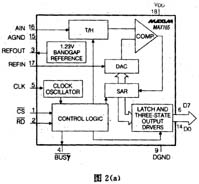

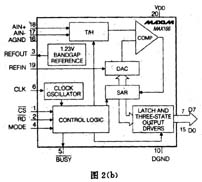

图2中,MAX165/166采用逐次逼近技术把一个被测模拟电压变为一个8位数字输出代码。一旦开始转换,MAX1645/166就用一个内部电容采样输入。采样保持如图3所示。A/D转换开始时,开关S1闭合,输入信号被采样。在CS和RD变低之后第3个时钟的下降沿,开关S1打开,输入信号被保持。保持电容CH要想充电至输入电压,必须等待最小两个时钟周期的时间。转换结束时,开关闭合,输入信号被采样。该采样保持器能采集电压上升率高达386mV/µs的模拟信号,因此其输入模拟信号频率可害50kHz。模拟开关的特性将影响采样保持电容的充电速度。模拟输入信号源内阻应低于2kΩ,这样有利于降低噪声和直流误差的影响。在转换期间,应尽量减小外部噪声源的影响,因此转换期间不应对芯片进行读写 *** 作。若转换时间远大于5µs,由于保持电容上的电荷轻微放电,将使转换精度略有下降。芯片上电后,内部DAC被锁定到满度量程的一半,采样保持器上的输入电压与DAC输出电压相比较,如果输入电压大于DAC输出电压,DAC的最高位为1,否则为0。每次比较后,逐次比较寄存器SAR将保存预定的结果,并确定下一次比较。每次保存的结果都将送不能超过DAC,8个比较周期后,将有8位数据存贮到SAR中,这时模拟输入电压的大小将非常接近于DAC的输出。转换完毕,转换数据在SAR中以锁存的方式输出。同时,BUSY变为高电平,DAC输出恢复为满度量程的一半,等待µP来读取

数据和进行下一次转换。

CS和RD逻辑信号用于对转换的初始化和从该芯片中读取数据。MAX165/166有两个通用接口方式:慢速存贮器接口方式(slow memory interface mode)和ROM接口方式(ROM interface mode)。另外,MAX166还有一种异步转换方式(asynchronous conversion mode),在该方式下,MAX166能进行连续的转换。

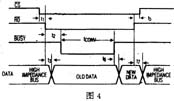

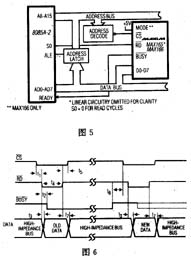

慢速存贮器接口时序图如图4所示。该方式用于和具有等待状态能力的µP接口(如8085A),插入等待状态至少为5µs。当CS和RD为低电平时,对芯片进行了一次存贮器读 *** 作,从而启动了一次转换,BUSY变低。通常,BUSY接不能超过µP的READY引脚,迫使µP进入待,在RD变低之后第止个时钟脉冲下降沿,采样保持器将把它所采样到的信号加以保持。转换结束时,BUSY信号变为高电平,新的转换数据将刷新输出缓冲存贮器。µP读取该数据即完成了对存贮器的读 *** 作,MAX165/166的转换速度很快,因而它所引起的µP的插入等待时间不会太长。对于工作速度较快的µP,如8085A-2,在每一个指令周期开始后测试READY输入引脚的状态。为了可靠地插入一个等待周期,在指令周期开始前BUSY应变为低电平。8085A-2提供一个SO状态信号接于MAX165/166RD输入引脚。当SO引脚变低时,表示将有一个对MAX165/166的读 *** 作。慢速存贮器接口方式连接图如图5所示。在这种方式下,实际上是利用RD和BUSY信号为作为与µP的“握手”信号,从而实现与µP的信息交换。

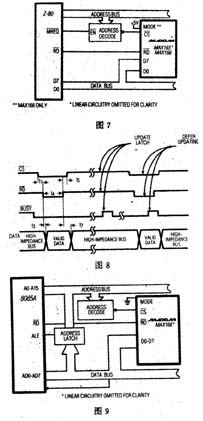

在ROM方式,µP不需插入一个待状态,其时序如图6所示。当RD和CS为低电平时,读 *** 作有效,上一次的转换数据被读取,同时开始新的转换。转换开始时,BUSY信号变为低电平,表示转换正在进行。在BUSY变为低电平以前而RD变为低电平以后第3个时钟的下降沿,T/H采样模拟信号。转换结束时,BUSY变为高电平。再一个读指令将该次转换的数据并启动下一次转换。注意,在BUSY恢复高是怦以前,RD和CS不能变低,否则不能启动转换,因此,只有在BUSY变为高电平以前,才可以对MAX165/166进行一次读 *** 作。ROM接口方式的连接图如图7所示。

如图MAX166的MODE引脚为低电平,MAX166进入连续读方式(conTInuousconversion moe),RD和CS信号只用于从转换器中读取数据,该方式也叫异步转换方式,其时序如图8所示。在这种方式下,MAX166相当于µP的一个ROM,其数据的读取将不受时钟的影响。在BUSY的上升沿,MAX166的输出锁存器的内容被刷新。当BUSY变高时,如果CS和RD为低电平。锁存器中的数据将不能被刷新,必须等到CS和RD变为高电平时,锁存器中的数据才能被刷新。

MAX166可以对差动信号进行转换,输入信号从AIN+和AIN-输入,差动输入电压范围为0~2VREF,如果AIN-接基准电压,AIN+端输入电压范围为1.23~3.69V。MAX166的差动输入功能有利于抑制低频共模干扰。转换开始时,AIN+处的电压被采样,该电压是以AIN-处对地电压相对稳定。否则,将增加转换误差。转换期间若AIN+发生变化,转换结果也将产生相同数量的误差。例如,在5µs的转换期间,如果有一个对地0.5V的60Hz的共模干扰,在转换结果中将有小于0.1LSB的误差。共模干扰引起的误差随共模电压幅度和频率的增加而升高。

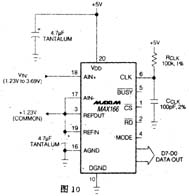

为了减小转换误差,MAX165/166要求基准源有小的直流和交流阻抗。MAX165/166的基准源分为内部基准源和外部基准源两种。外部基准源电路如图10所示。滤波电容可以有效地减小基准源的AC内阻。MAX165/166内部有一个1.23V的能隙基准电压,为了减小基准电压的内阻,通常在 REFOUT端与地之间接一个钽电解或铝电解与一个0.1µF的瓷片电容并联。如果选用外部基准,可把REFOUAT端接至VDD端,以禁止内部基准。

MAX1655/166既可使用内部时钟工作,也可使用外部时钟工作。当使用外部时钟时,外部振荡信号加在时钟引脚CLK上,内部电路将该时钟二分频来作为内部时钟信号。CLK引脚可由74HC系列或4000B系列芯片直接驱动,也可由一个LS系列TTL芯片通过一个5.6kΩ上拉电阻来驱动。外部时钟的占空比可在70/30和30/70之间变化。为了保证精度,时钟频率应低于4MHz。

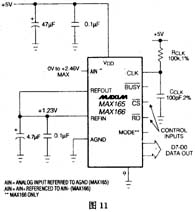

如果在CL引脚的外部接一个RC

网络,如图11所示,则MAX165/166可使用其内部振荡频率。在每次转换期间,CLK脚形成一个锯齿波。转换时,CCLK通过RCLK充电。转换结束时,通过一个内部开关放电。CLK引脚通过一个内部开关与VDD相连,内部振荡器停止工作。使用内部振荡源具有硬件简单的优点,但其振荡频率受RCLK和CCLK大小的影响,因此芯片的转换时间将受温度、RCLK及CCLK的影响。

3. 单极性模数转换电路

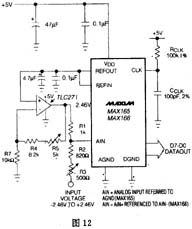

图12为由MAX165/166组成的单极性模数转换电路。由于 MAX165/166的偏置误差和满度误差很小,大多数情况下不必考虑这些误差。如果需要调节这些误差,可按下列步骤进行:

1.偏置误差的调节:可以使用一个运算放大器来调节偏置误差,如图12所示。调节R5即可改变偏置误差的大小。该运入实际上是一个基准电压源,输出电压的大小由R5来调节。通过调节偏置,使得在输入信号为0V时,ADC的输出码在00000000和00000001之间变化。

2. 满量程调节:满量程调节实际上是通过调节R3使AIN脚电压为2.445V时,ADC的输出码在11111110和1111111之间变化。

图12中,如果提高运放的输出电压,使其与模拟输入电压的最大值(+2.46V)相等,则模拟输入电压的范围将变为+2.46V~-2.46V,MAX165将由单极性转换变为双极性转换。SOC开发平台360元 豪华单片机开发系统498元 单片机学习板138 无线nRF-9E5模块100元 S3C44B0 ARM7开发板398元 Genius NSP通用编程器260元 Mini ARM Debugger330元 LABTOOL-48UXP2800元 S3C2410 ARM9开发板800

为了减小噪声,AIN引脚和AGND引脚应尽量短,也可使用屏蔽电缆或双绞线。同时,应尽量减小ADC地与信号源地的电位差,信号源内阻应低于2kΩ。线路板上的模拟地和数字地应采用一点接地的方法,电源和基准电压都应加旁路电容。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)