在40G/100G应用中使用10-Gbps收发器

本白皮书介绍向100G 接口过渡的关键推动力量,以及怎样利用FPGA 特有的功能来实现这一高速接口。数据中心以及核心网系统中新出现的40GbE 和100GbE 标准主要依靠FPGA 来链接本系统和其他协议的基础设备。StraTIx IV 器件提供的资源是前所未有的,例如逻辑、片内存储器和DSP 模块等,是唯一支持需要10G 收发器数据速率40G/100G 设计的FPGA 系列,其优异的低抖动性能满足了高速设计的需求。

引言

随着技术的进步,最新一代FPGA 提高了带宽,收发器数量越来越多,可以在单个器件中实现多种协议标准。FPGA 能够满足高速数据速率和带宽要求,新的目标市场定位在电信设备生产商上,这些生产商主要为40G 和100G 以太网(GbE) 开发新一代桥接应用和交换解决方案。

本白皮书介绍向100G 接口过渡的关键推动力量,以及怎样利用FPGA 特有的功能来实现这一高速接口。该协议的标准化进展对于其实现非常重要,使其最终能够降低关键昂贵元件的成本,以高性价比方式实现量产。符合公共接口标准有助于简化体系结构和器件工作。以太网10/100/1000 Mbps 和10 Gbps 接口定义已经完善,目前的标准处于10 Gbps 以上接口的起草阶段。

数据中心以及核心网系统中新出现的40GbE 和100GbE 标准主要依靠FPGA 来链接本系统和其他协议的基础设备( 这包括光纤通道、Infiniband 和SONET 等桥接和数据汇集等应用)。LAN 速率提高到千兆位,性价比最好的网络采用以太网作为主要的数据链路协议,具体实现由ASSP 和FPGA 完成。但是,当LAN、SAN 和MAN 速率超过10G 之后,高性价比的网络采用了多种数据链路协议,必须使用多种ASSP,或者

FPGA 作为桥接器件来提供高性价比解决方案。

满足40G/100G 需求

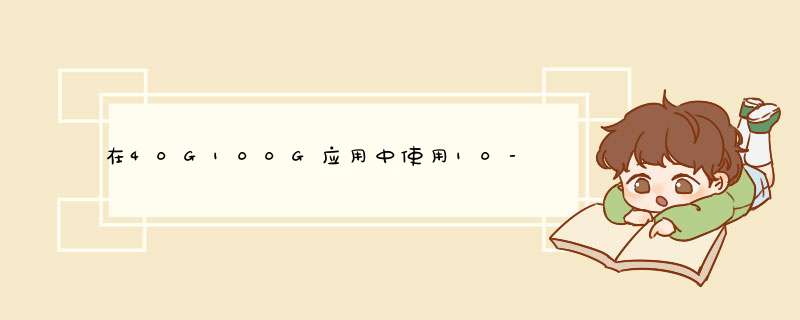

FPGA 经历了几个工艺代的发展,满足了40/100G 的需求,如图1 所示。在130-nm 工艺节点,FPGA 仅支持3.125 Gbps,而现在的40-nm 工艺节点能够支持10 Gbps 以上的数据速率。

图1. 工艺节点代

在40G/100G 应用中使用10-Gbps 收发器Altera 公司

2

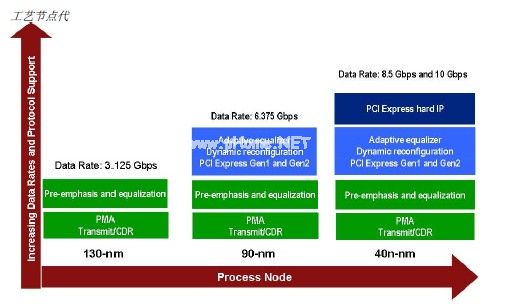

Altera® StraTIx® IV GX FPGA有32个嵌入式收发器,支持600 Mbps到8.5 Gbps的数据速率,另外16个收发器支持600 Mbps 到6.5 Gbps 的数据速率( 总共48 个速率达到6.5 Gbps 的收发器)。收发器包括物理编码子层(PCS) 和物理介质附加子层(PMA),这两个子层使StraTIx IV FPGA 能够实现标准和专用协议。图2 所示为StraTIx IV GX 收发器模块结构图。

图2. Stratix IV GX 收发器模块

从一个工艺代发展到下一工艺代, FPGA 密度几乎加倍,过渡到更小的工艺尺寸能够大大提高芯片中的系统集成度。增强FPGA 的功能虽然很重要,但更重要的是以更低的功耗实现最前沿的系统性能。Stratix IVFPGA采用了成熟可靠的工艺以及可编程功耗技术和动态片内匹配等体系结构创新技术来降低40G和100G应用的系统功耗,同时支持较高的系统带宽。

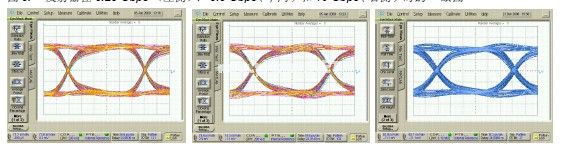

Stratix IV GX 收发器采用了先进的电源稳压和滤波技术,以降低发射器抖动,提高接收器抖动容限。因此,在实际系统链路中,收发器表现出优异的误码率(BER) 性能。发送和接收锁相环(PLL) 片内稳压器、敏感模拟电路的仔细隔离以及大量使用管芯和封装去耦合电容,都有助于为收发器提供可靠的电源分配方案,同时为模拟电路提供非常干净的电源。图3 显示了发射器在6.25 Gbps、8.5 Gbps 和10 Gbps 工作时的眼图。

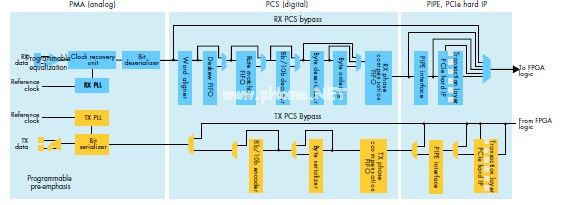

表1. 每个通道的收发器功耗( 仅PMA)

数据速率(Gbps) 40-nm 收发器功耗(mW)

3

图3. 发射器在6.25 Gbps (左侧)、8.5 Gbps( 中间) 和10 Gbps( 右侧) 时的“眼图”对100 Gbps 的需求网络带宽快速增长的主要动力来自xDSL、FTTx、WiMAX 和3G/4G 平台越来越多的宽带用户。IPTV、VoIP 和在线游戏等网络带宽应用,以及大量的在线用户访问视频点播网站,也影响了对更大带宽的需求。

今天,固网运营商以及电缆经营商的专网同时存在,他们通过互联网提供广播和按需点播节目,以及机顶盒视频节目。这类服务网络基于IP 技术,与节目内容来源和交付机制无关,在传送网的核心部分有巨大的带宽要求。

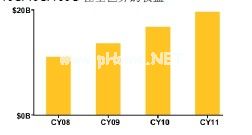

带宽迅速增长,而今后的需求将会越来越大( 图4)。目前的网络基础设施使用10GbE 协议,能够进一步提高容量,但是从数据网络拓扑结构的角度来看,每个10-Gbps 接口都需要单独的网络连接,因此,实现起来非常复杂。IEEE 802.3ad 所规定的链路汇集将多个低速通路绑定在一起,是简化数据网络拓扑的一种方法,但是该方法也有局限,还不是最佳解决方案。毫无疑问,随着40-Gbps 协议在核心网络的实施,人们对高速接口的需求不断增长,其应用也在加速。目前使用的协议是基于802.3ae 协议标准、单通路10G 网络汇集的形式。当前的解决方案基于SONET/SDH 和光传送网(OTN) 标准,但是,对40GbE 标准有明显的需求。人们也非常关注100 Gbps, IEEE 标准组织已经建议起草定义100GbE 接口。

图4. 对带宽的需求在增长:10G/40G/100G 在全世界的收益

40GbE/100GbE 接口的进展

IEEE 802.3高速研究组(HSSG)成立于2006年,研究100GbE接口协议的市场需要和标准的制定(如图5所示)。

2007 年,采用了包括40-Gbps 速率的另一建议。建议扩展了10G Base-R 带冲突检测的载波监听多路访问(CSMA/CD) 标准,以包括40 Gbps 和100 Gbps,其目标有:

■ 只包括全双工工作

■ 保留使用802.3 MAC 的802.3/ 以太网帧格式

■ 保留当前的802.3 标准帧长度规范

■ 支持优于或者等于10E-12 的 BER

■ 兼容OTN,适应WAN 应用。

在40G/100G 应用中使用10-Gbps 收发器Altera 公司

4

HSSG 于2008 年8 月提出最初草案,详细阐述了怎样实现该协议。对于评估该协议优缺点,在目前平台上进行原型开发等方面, FPGA 市场将扮演重要角色。

图5. 40GbE/100GbE 接口

802.3 标准的40G/100G IP 解决方案

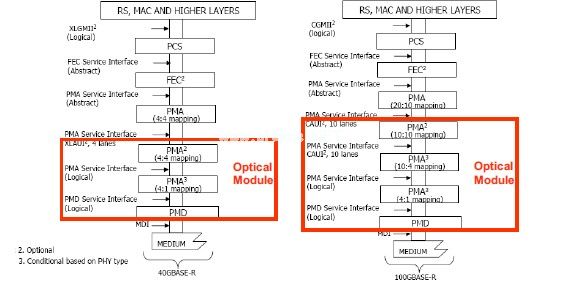

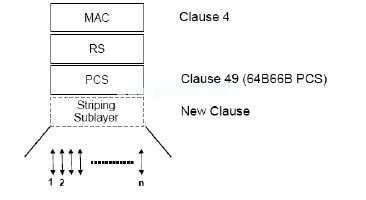

802.3ba 草案的MAC和PCS 部分以软核逻辑的形式在FPGA 架构中实现。如图6 所示,MAC特性与传统的以太网协议基本相同,不同之处在于100-Gbps 数据汇集。802.3 的PCS 实现采用64/66 编码方案,与802.3ae标准相同。

图6. 802.3ba 草案的MAC

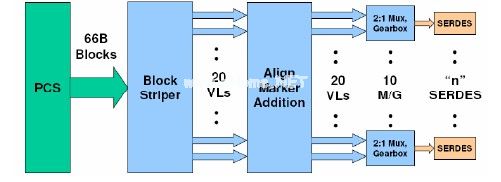

图7 显示了PCS 通道的发送通路。来自MAC 的数据首先被编码,成为64B/66B 块连续流,并被加扰。66

位加扰后的数据通过简单的罗宾带机制,分布到20 个虚拟通路(VL) 上。同时,周期性地在每个VL 上加上特殊的标记(66B 字)。接收PCS 模块使用这些标记来找到VL 中的数据,去掉偏移,重新排序,恢复100G汇集数据流。这20个VL终复用到10通路PMA,每个独立的PMA通路运行在10.3125 Gbps。数据通过10个100G-10 位接口(CTBI) 通路解复用。每个VL 中的对齐标记可以实现带内偏移机制。

5

图7. PCS 通道的发送通路

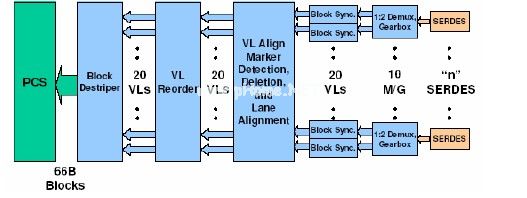

图8 显示了 100G PCS 模块的接收通路。接收通道将数据从10 个( 其中, n=10) 通路解复用至20 个VL。

接收通道去掉VL 偏移,进行对齐,恢复66B 数据流。接收通路上的每个VL 有自己的专用FIFO 缓冲,缓冲深度确定了设计的偏移容限。例如,深度为两个64 位字的FIFO 缓冲容限达到128 位偏移。

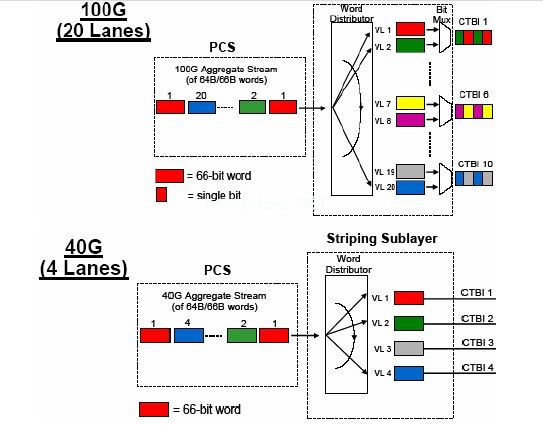

图9 显示了VL 的实现,只有当电(n) 和PMD (m) 通路数量不相等时才需要它。当器件收发器通路不对称时,VL 很容易实现这种转换。对于100G 实现,基于64B/66B 块,100G 汇集数据流被分到多个VL 中,对齐模块在每个VL 中插入。所采用的VL 数量与n 和m 通路的最少公共复用(LCM) 数成比例。实现100G 最多需要20 个VL,实现40G 最多需要4 个VL。虚拟通路支持接收通路进行偏移补偿,重新对齐VL,重新组合数据流,汇集为100G 或者40G 数据(64B/66B 块以正确的顺序排列)。

6

图9. VL 概念

100G MAC 解决方案

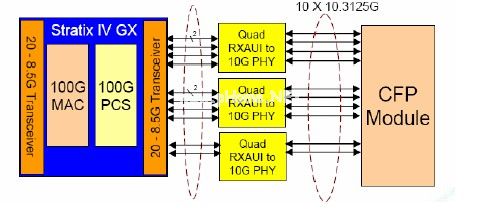

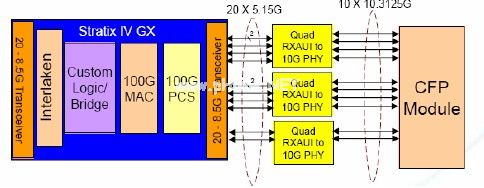

如图10 所示, Altera 的100G MAC 解决方案( 实现 20 个VL) 使用Stratix IV GX FPGA 和外部ASSP 或者定制ASIC 通过RXAUI( 简化的XAUI 接口,双倍速率运行) 进行连接,采用了新一代10G PHY 解决方案的MLD 特性。

Altera 公司在40G/100G 应用中使用10-Gbps 收发器

7

图10. 100G MAC 解决方案

100G MAC IP由Altera合作伙伴MoreThanIP和Sarance提供,符合802.3ba标准。Altera致力于同合作伙伴的密切协作,提供100G 解决方案。

全面的系统解决方案在系统侧接口, Stratix IV FPGA 通过20 个数据速率高达6.375-Gbps 的通路,使用Interlaken 协议提供100G 芯片至芯片接口。如图11 所示,全面的解决方案为线路侧至系统侧提供专用100G 数据通路。灵活的FPGA 使用户能够在系统侧使用专用总线接口,连接专用接口和业界标准Interlaken 接口。Altera 的Interlaken解决方案兼容Interlaken Alliance 规范。

图11. 全面的系统解决方案

这一推荐的解决方案利用了当前的辅助系统和第三方MLD复用PHY来提供40-nm技术节点的业界标准100G平台。Altera 致力于为100G 网络平台的实现提供最佳解决方案。

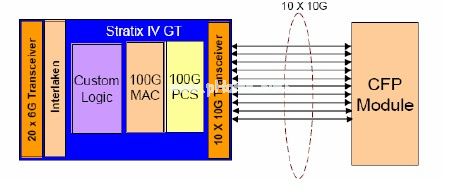

最佳100G 系统解决方案

图12所示的最佳100G系统解决方案采用了领先的收发器技术,工作在10 Gbps以上,不需要具有MLD特性的外部 10G PHY 器件。这一方案是真正的单芯片FPGA 100G 解决方案, 100G CFP 光模块可直接与AlteraStratix IV GT FPGA 连接。Stratix IV GT 器件使用户能够在单片FPGA 架构上灵活地采用流量管理、数据查询

8

版权© 2009 Altera 公司。保留所有版权。Altera、可编程解决方案公司、程式化Altera 标识、专用器件名称和所有其他专有商标或者服务标记,除非特别声明,均为Altera 公司在美国和其他国家的商标和服务标记。所有其他产品或者服务名称的所有权属于其各自持有人。Altera 产品受美国和其他国家多种专利、未决应用、掩模著作权和版权的保护。Altera 保证当前规范下的半导体产品性能与Altera 标准质保一致,但是保留对产品和服务在没有事先通知时的变更权利。除非与Altera公司的书面条款完全一致,否则Altera 不承担由使用或者应用此处所述信息、产品或者服务导致的责任。Altera 建议客户在决定购买产品或者服务,以及确信任何公开信息之前,阅读Altera 最新版的器件规范说明。

101 Innovation Drive

San Jose, CA 95134

在40G/100G 应用中使用10-Gbps 收发器Altera 公司和数据处理等功能。在目前的产品中, Stratix IV GT FPGA 含有32 个能够运行在11.3 Gbps 的收发器,另外16 个支持6.5 Gbps 数据速率的收发器( 总共48 个)。

图12. 最佳100G 系统解决方案

结论

Stratix IV 器件系列满足了市场对高密度、高性能和低功耗的需求。它是唯一能够实现最佳40G/100G 解决方案的系列FPGA。在40-nm 工艺节点, Stratix IV FPGA 提供的资源是前所未有的,例如逻辑、片内存储器和DSP 模块等。此外, Stratix IV FPGA 支持40G/100G 设计,这些设计需要10G 收发器,要求抖动非常低,以满足高速设计要求。该器件系列非常适合满足40G/100G 设计需求,现在已经开始供货。

致谢

■ Rishi Chugh,产品营销经理,高端器件营销, Altera 公司。

■ Seyi Verma,产品营销经理,高端FPGA, Altera 公司。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)