作者:Chen Yan

随着近年来工业互联网蓬勃发展,智能化信息化进程逐步加快,而EtherCAT技术由于其具有通讯的高性能,硬实时性能,灵活的拓扑结构,简单、低成本及充分的开放性,以EtherCAT为代表的工业以太网的发展势头远超现场总线,逐渐成为未来工业互联网的主流应用。

EtherCAT是使用100Mbit/s 全双工的Ethernet通讯。通常由EtherCAT从站控制器(EtherCAT Slave Controller,ESC)和物理层接口PHY实现EtherCAT的应用。ESC通常会支持PHY使用MII,RMII和RGMII接口,由于RMII和RGMII接口包含TX FIFO,会增加EtherCAT从站设备的传输延时,同时也会引入抖动,所以一般不建议在EtherCAT应用中使用,本文主要讨论PHY的MII接口的硬件配置。

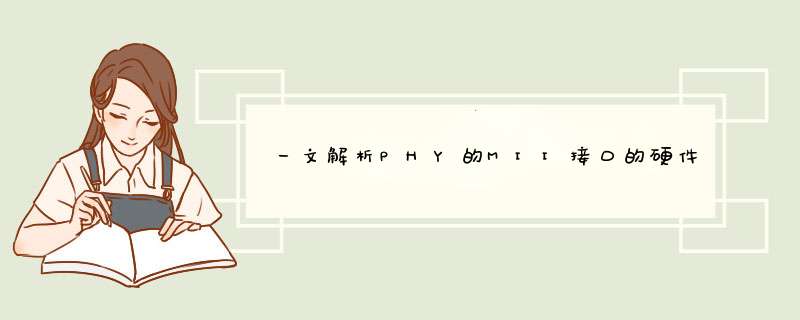

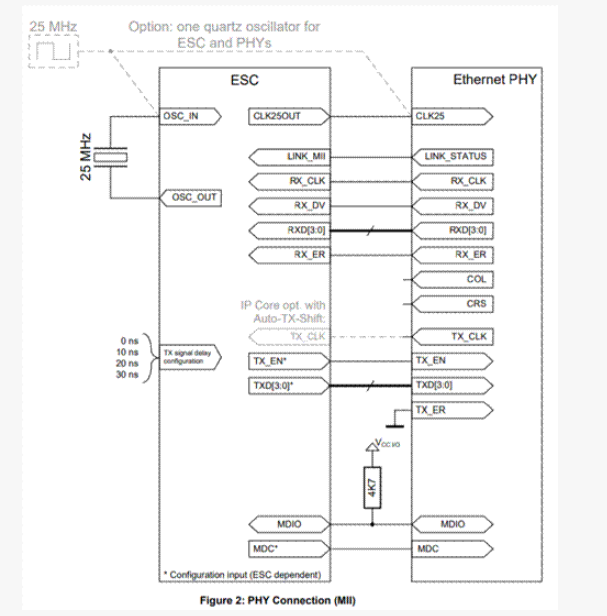

下图是ESC和PHY MII之间的连接关系的示意图。ESC和PHY之间的时钟必须保持一致。LINK_STATUS是一个LED输出信号,用来指示100Mbit/s全双工的通讯连接状态。

DP83822 是一款低功耗单端口10/100Mbps以太网PHY。它提供通过标准双绞线电缆发送和接收数据或者连接到外部光纤收发器所需的所有物理层功能。此外,DP83822还可通过标准MII、RMII或RGMII接口灵活地连接到MAC。

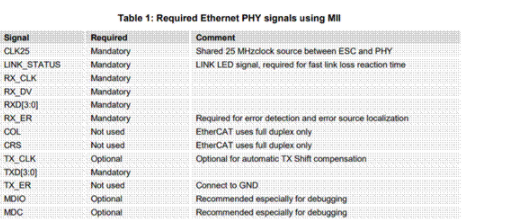

DP83822的部分接收路径功能pin脚可以用bootstrap的方式将PHY配置为特定的工作模式,这些pin脚的电压值会在上电或者Reset的时候被检测到,从而完成PHY的配置。DP83822可以通过一个4电平的bootstrap电路来配置,bootstrap pin脚需要增加推荐值的上拉或者下拉电阻来设置电压,从而配置为某种特定模式。

下图是DP83822的bootstrap电路示意图,一部分bootstrap pin脚内置50kΩ的上拉电路,另一部分的bootstrap pin脚内置9kΩ的下拉电阻。通过外加上拉电阻RH和下拉电阻RL可将该bootstrap pin配置为特定模式。

下表是应用于EtherCAT MII的DP83822的bootstrap配置示例,配置pin29将地址的最低位PHY_AD0配置为0(作为地址位配置的示例)。此外,配置pin27将LED 0和LED 1配置为EtherCAT应用要求的功能。其他bootstrap pin保持默认值即可。

PHY_AD0(1) 1.9k PD (0 0) FX_EN(0)

PHY_AD0(0)

PHY_AD1(0)

PHY_AD2(0)

PHY_AD3 (0)

PHY_AD4(0)

LED speed(0) 13k PU 1.9k PD(10) LED_CFG(0)

LED speed(1)

AMDIX enabled

RMII disabled

FX_EN AN_EN AN_1 AN_0 0 1 1 1 à Advertised Modes, 100BASE-TX and 10BASE-Te, Half and Full-Duplex

LED_SPEED LED_CFG[0] 1 0 à LED 0(Good link/blink activity) LED 1 (show speed (100Mbps/10Mbps)

PHY address 0 0 0 0 0 à serial management interface address 0

DP83826 能够提供很低的延迟和低功耗,并支持 10BASE-Te、100BASE-TX 以太网协议,可以满足实时工业以太网系统中的严格要求。该器件包含两种可配置模式:使用通用以太网引脚的 BASIC 标准以太网模式,以及支持标准以太网模式和多个工业以太网现场总线应用的ENHANCED以太网模式。由于在BASIC模式下配置EtherCAT应用需要通过软件对寄存器进行写 *** 作,而ENHANCED模式可完全通过bootstrap pin来完成配置,所以下述主要介绍用ENHANCED模式配置EtherCAT。

DP83826的bootstrap电路一共由两个电平,如下图所示,一部分bootstrap pin脚内置10kΩ的上拉电路,另一部分的bootstrap pin脚内置10kΩ的下拉电阻。通过外加2.49kΩ的上拉电阻RHI和下拉电阻RLI可将该bootstrap pin配置为特定模式。

下表是DP83826 bootstrap pin在BASIC和ENHANCED模式下的功能说明,最后一列是配置DP83826为ENHANCED模式下的EtherCAT应用。

1 (enable)

编辑:hfy

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)