一种实用的VXI总线接口设计

随着计算机技术与超大规模集成电路技术的发展,对以计算机为主控机的自动测试系统的要求越来越高。在vme总线基础上发展起来的vxi总线正适应了这种发展的要求和趋势,它具有体积小、重量轻、速度快、电磁兼容性好、定时准确、可靠性高、软件标准化程度高、 *** 作灵活方便等很多优点,因此发展十分迅速。国外已大量应用并有许多商业产品问世,国内也在积极开发引进。我们在研制某新型飞机火控雷达系统的检测设备的过程中,组建了vxi总线雷达自动检测系统。在研制该系统过程中,我们开发了一种利用cpld和双口ram设计的寄存器基vxi总线仪器接口电路,下面我们就这一接口电路做一介绍。

1 接口的功能

(1)产生本板复位信号,包含程序复位和硬件复位;

(3)产生vxi总线的数据传输应答信号dtack*、数据总线使能信号dben*和数据传输方向控制信号dir;

(4) 具有中断请求功能。

2 电路设计

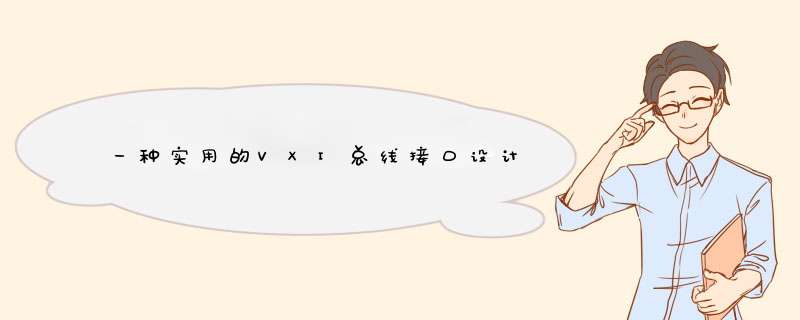

作为寄存器基的接口电路,它具有配置寄存器和相关寄存器,为a16\a24接口,执行d16功能。总线隔离电路比较简单,可用双向总线连接器74ls245实现,在这里不做详细地介绍。vxi总线的接口译码电路利用一片xilinx公司的xc95108-pc84cpld完成,利用双端口ram—idt7024来实现配置寄存器和器件相关寄存器。图1为接口功能结构图。

2.1 vxi总线接口译码电路

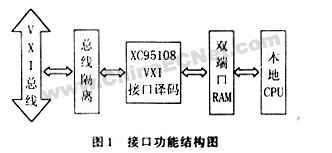

vcpld是可由用户进行编程实现所需逻辑功能的数字集成电路,它具有高性能、高集成度、高度灵活适用等诸多优点。使用cpld,可简化电路设计、缩小系统规模,提高电路可靠性,还能缩短开发周期。xc95108-pc84cpld是xilinx公司的第三代产品 ,它由快速连接开关矩阵连接的6个完全相同的功能模块组成,具有108个宏单元,集成了2400个可用逻辑门,传播延时为5 ns,用它编程信息不易丢失,可电擦除。图2为接口译码原理框图,该接口分为地址译码、总线 *** 作控制译码两部分,其中地址译码又分为a16地址选通和a24地址选通两部分。它们都集成在一片xc95108-pc84cpld里。

vxi总线选择使用16、24或32位3种地址接口,不同的地址范围是短地址16位,标准地址24位以及扩展地址32位。地址宽度由地址修改码am0~am5决定,本接口选用短地址和标准地址。短地址使用地址线a01~a15,地址修改码为29h或2dh;标准地址使用地址线a01~a23,地址修改码为39h、3ah、3dh、3eh。作为寄存器基的接口,数据传输 *** 作过程如下:在iack*为高时,主模块用地址选通线as*下降沿通知接口可获取地址信息。当寻址到本接口时,则打开数据通道,并在数据选通线ds1*或ds0*的下降沿,根据读写信号线write*的状态,进行数据的读或写;并且通过数据传输应答线dtack*为低有效作为应答信号。

作为a16\a24接口,它必须完成a16\a24接口的寻址要求。它包括vxi总线a16寄存器和a24寄存器寻址电路、vxi总线a16寄存器和a24寄存器、vxi总线a16\a24总线 *** 作控制电路。在电路中,当am16码符合a16器件的地址修改码的要求并且逻辑地址与本器件的八位逻辑地址开关相符时,选中本接口为a16接口。当am24码符合a24接口的地址修改码的要求并且偏移地址也与本接口的偏移地址相符时,选中本接口为a24接口。

接口中a16选通信号a16*(上标*表示低电平有效)有效的条件是:

a16*=(not a15) or (not a14) or (a13 xor q7) or (a12 xor q6) or

(a11 xor q5) or (a10 xor q4) or (a9 xor q3) or (a8 xor q2)

or (a7 xor q1) or (a6 xor q0) or (not am0) or am1 or (not am3)

or am4 or am5 or (not iack*) or (not lword*)

其中q7~q0表示八位逻辑地址的状态。

接口 中a24选通信号a24*有效的条件是:

a24*=(a23 xor b15) or (a22 xor b14) or … or (an xor bn-8)

其中b15~bn-8表示偏移地址的状态。

总线 *** 作控制电路随时监视寄存器选通信号a16*,a24*和数据选通信号ds0*~ds1*,产生数据总线使能信号dben*、数据传输方向控制信号dir和总线数据传输应答信号dtack*。这些信号的译码方程为:

ds*=ds1 and ds0

eion*=(a16* or ds*) and (a24 or ds*)

dir=eion* or (not write*)

dtack*=eion*

这些逻辑表达式都很容易在cpld里实现。a16器件寄存器和a24寄存器均采用双端口ram—idt7024来实现。双端口ram的一边接入vxi总线,另一边则挂到本地cpu上,如此本地cpu就可通过这些寄存器与系统中的其他器件进行数据交换。

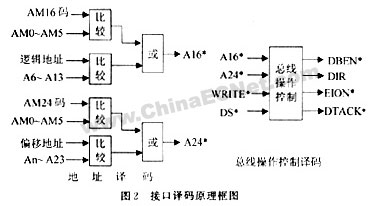

2.2 双端口ram电路

双端口ram—idt7024有两套独立的地址线、数据线、读写线、忙线和片选线,分别面向vxi总线及本地cpu,ram则是一套,有4 k×16个存储单元。它允许2套同时读写不同的ram单元和同时读同一ram单元;在其他情况下访问同一ram单元时,将会引起冲突,无效的一方以忙线busy*为低,通知本方这次读写无效。对于面向vxi总线部分,采用a16寄存器的地址线a01~a05和a24寄存器的地址线a01~an-1在经过其相应的选通信号a16*和a24*使能的锁存器后,并接到双端口ram的地址线上。这样可保证同一双端口ram可既可作为a16寄存器,又可作为a24寄存器;但是最低的64个字节的寄存器地址是相同的,应分配给a16寄存器,高于此64字节的寄存器都可作为a24寄存器 。配置寄存器的内容由本地cpu上电初始化程序一次写入,供vxi总线读取。为了解决ram的冲突问题,面向本地cpu的忙线为cpu外部最高级中断源,一旦发生冲突,将通过中断服务设置标志,通知本地cpu重新读写。

器件具有64个字节的a16器件寄存器,按地址从低到高可分为2类:器件配置寄存器和器件相关寄存器。配置寄存器共4个,分别是识别/逻辑地址寄存器,器件类型寄存器,状态/控制寄存器和偏移寄存器。读出这些寄存器可了解器件的基本配置情况和状态,向这些寄存器写入可完成对器件的基本控制功能。器件在a24地址空间还有k字节的相关寄存器,相关寄存器的用法由用户自己定义。所有这些寄存器均由双端口ram来实现。接入总线需要有数据线d0~d15,片选线eion*及读写信号线write*。采用双向缓冲器将器件板上的数据总线和vxi背板上的数据总线隔开,用数据传输方向控制信号dir控制双向缓冲器的方向,用总线 *** 作控制电路产生的一个数据总线使能信号dben*来使能该双向缓冲器,使它在有别的器件对本器件进行读写 *** 作时才打开而在其他时候关闭。

3 结论

采用cpld和双端口ram后使vxi总线接口电路得到了极大的简化,且a24寄存器的大小可由需要增加双端口ram的片数而定,可以实现在系统编程进行修改,具有很大的灵活性。该接口经实用证明,性能可靠,使用方便,具有良好的通用性。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)