电路的功能

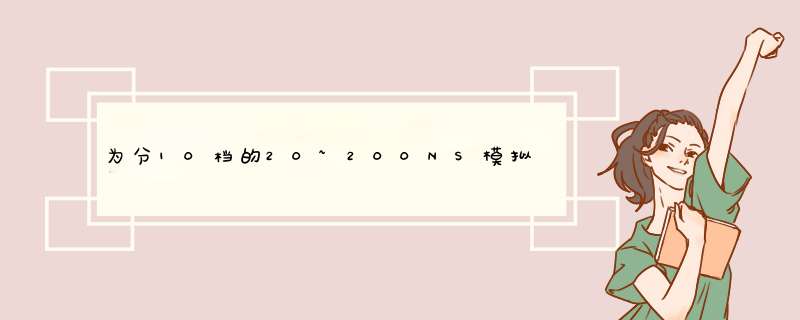

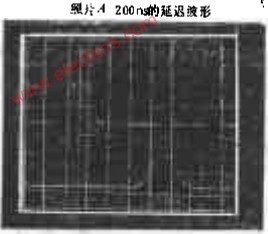

模拟信号的延迟大多采用BBD器件,可获得数毫秒的延迟时间,但其S/N不好,应用范围受到限制。延迟时间较短时,也可使用同轴电缆,但必须占用较大空间,因此往往不太现实。本电路使用了集中电路网络构成的小型延迟线,以20NS为一档,在20~200NS范围内使模拟信号延迟。

电路工作原理

由线圈L和电容器C组成集中电路,若以特性阻抗端接,不会有反射,电路网络作为低通滤波器使用。

所谓特性阻抗端接,就是从延迟线的输出、输入端看输入、输出的阻抗,本电路为350欧。

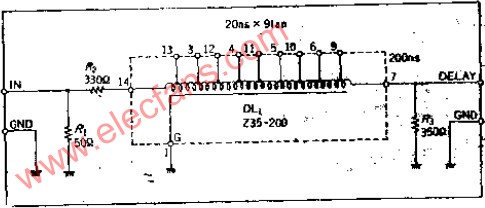

照片A救出了输入模拟信号脉冲从200NS的分接点输出波形约有200NS的滞后,20~180NS分接点的输出波形也相似。

本文地址:http://www.elecfans.com/arTIcle/analog/2010/20100510217281.html

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)