数据带宽=(总线频率×数据位宽)÷8

B表示带宽,F表示存储器时钟频率,D表示存储器数据总线位数,则带宽为:

B(峰值带宽)=F(时钟频率MHz)×D(总线位数bit)/8

例如,PC-100的SDRAM带宽计算如下:

100MHz×64bit/8=800MB/S

由于SPI(serial peripheral interface)总线占用的接口线(4根)少,通信效率高.eg:外接M25P64型号的SPIFLASH时,SPI总线的最大传输速率为75MHz/8=9375KB/S,因为该SPIFLASH的频率:75 MHz.普通IIC总线传输速率为10kbps--400kbps.并且SPI支持大部分处理器芯片,因而是一种理想的选择.

SPI通信是串行发送或接收数据的,即一位一位的发送和接收(按位传输),且传输一般是高位MSB在前,低位LSB在后.

SPI模式可以允许同时同步发送和接收8位数据,不同于IIC.IIC只有一条数据线,所以IIC每次只能发送数据或传输数.SPI是利用4根信号线进行通信的串行同步接口协议,包括主/从两种模式.4个接口信号为:串行数据输入(MISO,主设备输入、从设备输出)、串行数据输出(MOSI,主设备输出、从设备输入)、移位时钟(SCK)、低电平有效的从设备使能信号(CS).SPI最大的特点是由主设备时钟信号的出现与否来确定主/从设备间的通信(不想传数据时可采用停止时钟的方式).一旦检测到主设备的时钟信号,数据开始传输.

SPI在远距离传输中很少用到,主要因为其抗干扰能力差,可靠传输距离只有1—3m.SPI

采用的是单端非平衡的传输方式,即传输的数据位的电压电平是以公共地作为参考的.在这种传输方式中,对于已进入信号中的干扰是无法消除和减弱的.而信号在传输过程中总会受到干扰,而且距离越长干扰越严重,以致于信号传输产生错误.在这种条件下,信号传输就变得毫无意义了.另外,由于单端非平衡传输方式以公共地作为参考点,地线作为信号回流线,因此也存在信号电流.当传输线两端的系统之间存在交流电位差时,这个电位差将直接窜到信号中,形成噪声干扰.所以,为了解决抗干扰问题,通常采用平衡传输(balanced transmission)方式,这里采用比较常见的RS-422.

1. SPI器件的主从模式设置

SPI接口的器件,分为主设备(Master)和从设备(Slave).主设备产生时钟信号,从设备使用主设备的产生的时钟.主设备能主动发起数据传输.单片机的SPI控制寄存器SPCR中的MSTR位就是用来选择单片机在传输中是作为主设备还是从设备的.MSTR设为1时为主设备,设为0的时候为从设备.对单片机来讲管脚SS的电平也会影响SPI的工作模式,在主设备模式下,如果SS是输入且为低电平那么MSTR会被清零,设备进入从模式.MISO信号由从机在主机的控制下产生.

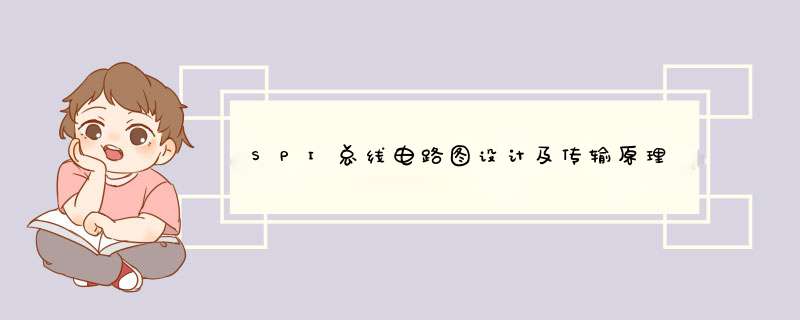

下图是由一个主机对接一个从机进行全双工通信的系统构成的方式.在该系统中,由于主机和从机的角色是固定不变的,并且只有一个从机,因此,可以将主机的SS端接高电平,将从机的SS端固定接地.

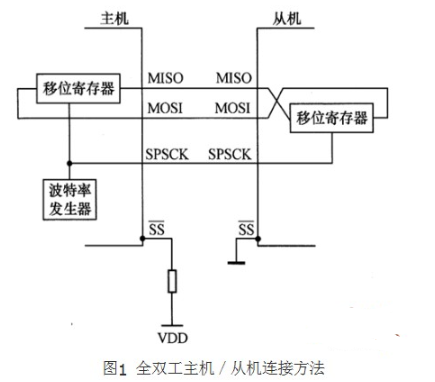

下图是一个主机和多个从器件

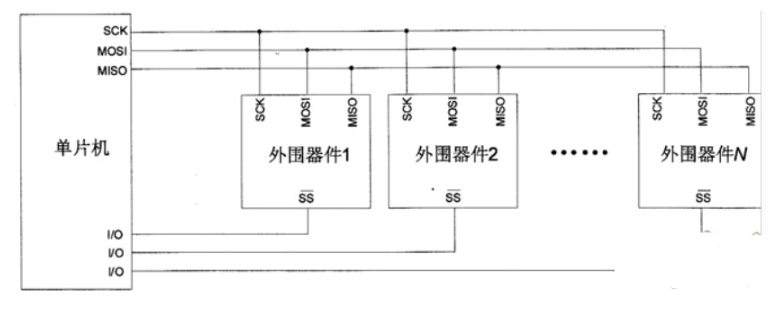

采用由三个单片机互相连接构成多主机通信系统连接方法如下:

2. SPI器件的时钟极性和相位设置

所有的SPI设备都采用相同的接口方式,可以通过调整处理器内部寄存器改变时钟的极性和相位.由于SPI器件并不一定遵循同一标准,比如EEPROM、DAC、ADC、实时时钟及温度传感器等器件的SPI接口的时序都有所不同,为了能够满足不同的接口需要,采用时钟的极性和相位可配就能够调整SPI的通信时序.

SPI主机与之通信的从机的时钟极性和相位应该一致.可以先看看另一篇博文,专门讲解了时钟极性和相位:http://www.cnblogs.com/jason-lu/arTIcles/3713319.html

SPI数据传输的模式根据时钟的极性和相位有四种组合,这就是四种不同的传输模式.分别称为模式0,模式1,模式2,模式3.有的SPI接口的器件只支持几种模式,比如SPI接口的EEPROMAT25128可以工作于模式0和模式3.在实际使用中需要设置为和外围器件兼容的模式.

设置举例:

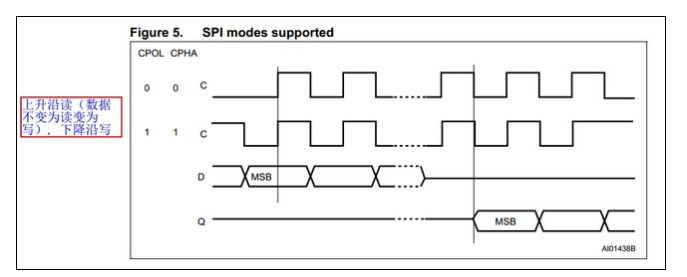

M25P64数据手册上给出的时钟的极性和相位和数据读写的对应的时序

如上图所示:

时钟极性和相位都是0时,上升沿为前沿,数据稳定被采样(锁存),下降沿为后沿,被写入SPI总线.

时钟极性和相位都是1时,上升沿为后沿,数据稳定被采样(锁存),下降沿为前沿,被写入SPI总线.

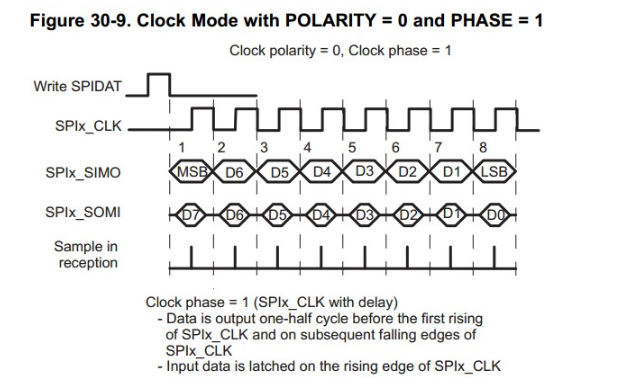

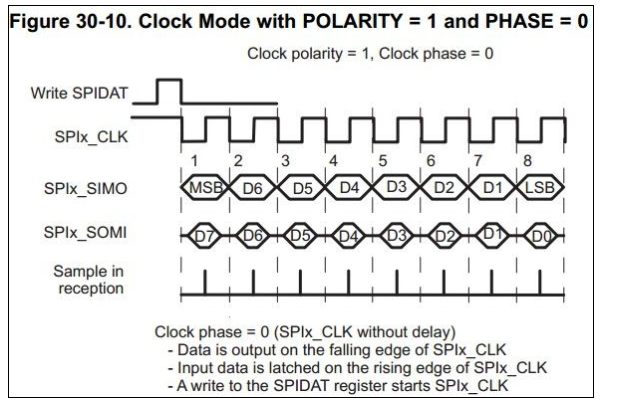

和M25P64数据手册上给出的时钟的极性和相位和数据读写的对应的时序匹配的omapl138数据手册上给出的时序

注:

从机对时序的响应和主机对时序的响应相同但要比主机反应迟钝

图30-9和图30-10的区别:虽都表示时序上是下降沿写上升沿读,但30-10表示片选一拉低数据就被写出,而30-9表示当片选拉低后还要等时钟的下降沿来临数据才被写出.

数据在上升沿被锁存

所以对应的程序:

//SPIFMT0寄存器 bit 8-15 是配置时钟频率,bit16是时钟延时,bit17是时钟极性(在高电平触发还是低电平触发)

SPI1->SPIFMT0 = 0x00020608;//startware配置 //SPI1->SPIFMT0 = 0x00010208;(ok logicpd配置)

3. SPI的传输原理

SPI设备传输数据过程中总是先发送或接收高字节数据,每个时钟周期接收器或收发器左移

1位数据(SPI总线是按位传输的).对于小于16位的数据在发送之前必须左对齐,如果接收的数据小于16位则采用软件将无效的数据位屏蔽,如图1所示.对应的C代码:

主机和从机都有一个串行移位寄存器,主机通过向它的SPI串行寄存器写入一个字节来发起一次传输.主机的移位寄存器通过MOSI信号线将字节传送给从机的移位寄存器,从机也将自己的移位寄存器中的内容通过MISO信号线返回给主机的移位寄存器中(如下图所示).这样,两个移位寄存器中的内容就被交换.外设的写 *** 作和读 *** 作是同步完成的.

如果只进行写 *** 作,主机只需忽略接收到的字节;当然,若主机要读取从机的一个字节,则应该发送一个空字节来引发从机的传输.

SPI的传输实际上相当于两个八位移位寄存器首位相连.每个时钟周期,数据从一个设备的移位寄存器移出,同时移入了另一个寄存器.八位数据全部移出时,两个寄存器就实现了一次数据交换.因此,SPI的发送和接收是同时进行的,实际都是发送一个字节发起的,只不过需要接收的时候发送的是一个我们不关心的任意字节.

4. SPI传输示例编程

当主机发送一个连续的数据流时,有些外设能够进行多字节传输.多数具有SPI接口的存储芯片就以这种方式工作.在这种传输方式下,从机的片选端必须在整个传输过程中保持低电平.此时,一次传输可能会涉及到成千上万字节的信息,而不必在每个字节的数据发送的前后都去检测其起始位和结束位(片选拉低开始,片选拉高结束),这正是同步传输方式优于异步传输方式的原因所在.

针对外设是M25P64 外设的SPI的传输

方式:命令字(一个字节)+FLASH的地址(三个字节)+要发送或接收的数据(n个字节)

/* Send read command to the flash (one byte) */

tx_data = 0x03; //SPI_FLASH_READ,这是单字节指令代码

SpiTransfer(&tx_data, &rx_data, 1);

/* Send the address to start reading from (3 bytes) ,共24位*/

addr[0] = (unsigned char)(flashAddr >> 16);

addr[1] = (unsigned char)(flashAddr >> 8);

addr[2] = (unsigned char)flashAddr;

len = 0;

while (len < sizeof(addr))

{

SpiTransfer(&addr[len], &rx_data, 1);

len++;

}

/* Read all the bytes */

len = 0;

while(len < size)

{

SpiTransfer(&tx_data, destAddr, 1);

destAddr++;//共20个字节,一个字节一个字节放入

len++;

}

命令字:

// numonyx spi flash commands. #define NUMONYX_CMD_WREN (0x06) #define NUMONYX_CMD_WRDI (0x04) #define NUMONYX_CMD_RDID (0x9F) #define NUMONYX_CMD_RDSR (0x05) #define NUMONYX_CMD_WRSR (0x01) #define NUMONYX_CMD_READ (0x03) #define NUMONYX_CMD_FAST_READ (0x0B) #define NUMONYX_CMD_PAGE_PROG (0x02) #define NUMONYX_CMD_SEC_ERASE (0xD8) #define NUMONYX_CMD_BULK_ERASE (0xC7) #define NUMONYX_CMD_RD_ELEC_SIG (0xAB)

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)