九十年代以来,我国从俄罗斯相继引进了不同型号的导d,同时,也引进了配套的导d测试系统。近年来,随着导d测试系统寿命的临近,在国内现有技术基础上延长其使用寿命是维修保障部门的重要任务。为此研制导d测试系统关键部件的备件,成为延长系统寿命的一个重要手段。

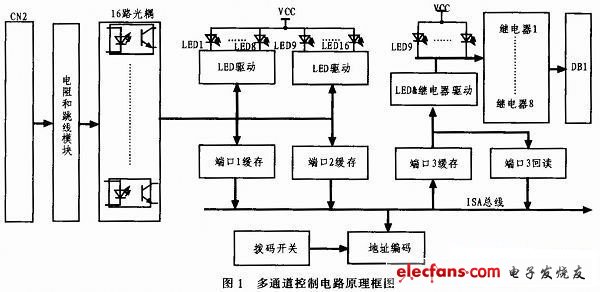

文中依据某型导d测试设备的要求,设计并研制了基于ISA总线的多通道控制电路:该电路集成了16 路光电隔离输入通道和8路单刀双掷(SPDT)继电器输出通道,每一路输入或输出通道都配有指示灯实时标识目前的状态。在测试系统中,该控制电路可在 ISA测试总线的控制下将数据信号、指令信号和电源信号分配至不同电路,实现对导d的自动测试。实际应用结果表明,研制的多通道控制电路达到设计要求,可完全替代俄制电路。

1 ISA总线简介

1)数据总线SD7~SD0 SD7~SD0为8位双向三态数据总线,在芯片和主接口间传输命令、数据和状态。SD7为最高位。

寄存器选择引脚为SA9~SA4、SW DIP-6(板基址011001)和AEN#.这些引脚决定转换是否响应I/O周期,当AEN#为逻辑低电平且SA9~SA4与6位拨动开关值完全匹配时,内部产生一片选信号使转换响应I/O周期。

2)地址信号SA3~SA0 I/O读写 *** 作时作为转换电路上FPGA芯片内的寄存器选择信号。

3)读写信号IOR#,IOW#写 *** 作中,转换在IOW#上升沿锁存数据。读 *** 作中,当IOR#有效时,转换模块直接驱动8位数据线。

4)中断信号INTR 中断状态寄存器某使能中断为真时,INTR有效。对INTR的有效声明没有最小脉宽要求。

5)IO通道准备好信号IOCHRDY IO CHRDY变低表明当前I/O周期需要被延长。写周期中,当数据从ISA总线上被锁存时IO CHRDY变高。读周期中,数据有效时IO CHRDY变高。进行寄存器读写时IO CHRDY被拉低。IO CHRDY引脚用集电极开路逻辑门驱动,因此,此信号会由一个内部上拉电阻上拉至逻辑高电平。

6)复位信号RESET RESET信号有效时触发转换模块使FPGA硬重启。

2 工作原理

如图1所示,基于ISA总线的多通道控制电路由地址编码、继电器通道、光耦隔离电路等部分组成。其工作原理如下:电路工作时,首先将ISA总线的高位地址与板载拨码开关设定的板基地址进行比较,其低位地址通过地址编码选通3个读通道和1个写通道。读通道为端口1缓存、端口2缓存、端口3回读通道,写通道为端口3缓存通道。当工控机需要读取反馈信号时,反馈信号从接口CN2输入16 路光耦,通过电阻和跳线模块设定其工作模式,数据写入端口1缓存和端口2缓存供工控机读取;同时每路光耦对应一个LED,实时显示目前工作状态。当工控机需要将信号发出时,工控机将数据写入端口3缓存,经过继电器驱动器驱动后,控制8路继电器,由DB1输出;同时,每路继电器对应一个LED,实时显示目前状态。写入端口3的数据还可以通过回读地址将其读回,回读地址与写地址相同。

3 电路设计

按照工作原理可将多通道控制电路分为地址编码电路、继电器控制输出通道电路和光耦隔离输入通道电路3部分。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)