在现有LED显示屏发送卡的基础上,这里设计了一种无外接存储体的LED显示屏发送卡,如图1.

图1 LED显示屏发送卡原理图

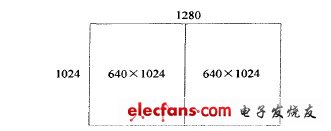

该发送卡由DVI模块、FPGA控制器、两路千兆网输出模块构成。DVl解码芯片将解码得到的数据和控制信号传给FPGA控制器,FPGA通过内部的RAM 进行缓存,并做了更换时钟域和位宽变换的 *** 作,然后将处理后的数据通过千兆网输出。对分辨率1280×1024,刷新频率为60Hz的实时视频源,这里采用垂直分区的方法,即将满屏数据平均分成两路千兆网输出,每一路千兆传输640X 1024,如图2所示。

图2视频数据分区图

实现方法

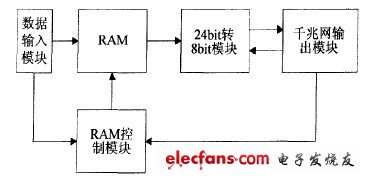

由图1的基本框图看出,该发送卡的设计除了搭建好硬件平台外,最重要的是FPGA控制器内部程序的设计。发送卡的FPGA控制器内部原理框图如图3所示。

图3 FPGA控制器的内部原理框图

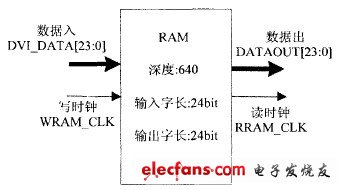

FPGA控制器的内部逻辑包括数据输入模块、双口RAM 及其控制模块、24bit转8bit模块、千兆网输出模块。数据输入模块将输入的DVI信号(包括数据、时钟、使能、行场同步信号)分配给后端的RAM 和RAM 控制模块,并控制着整个系统的同步;RAM控制模块控制RAM 的读写 *** 作,尤其是对开始写、写停、开始读、读停这4个状态的控制:从RAM 输出的数据经过并串转换后传输给千兆网输出模块,千兆网输出模块则按照一定的网络格式将接收到的数据进行打包输出 。图2提到的将数据分区发送,该方法能够将满屏数据平均分成两路千兆网输出。以下就以垂直分区的方法分析其数据流向、时钟变化和传输时间差。对于一路千兆网数据而言,采用1个双口RAM设计,RAM 的深度设置为640,输入和输出字长均设置为24bit,读写时钟和使能分别独立,如图4所示。

图4一路千兆网数据传输的双口RAM 配置

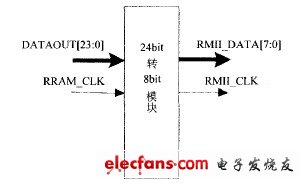

其中,数据输入和写时钟分别为DVI解码芯片解码后的24bit图像数据DVI-DATA [23:0]和时钟WRAM_CLK,读RAM 的时钟为千兆网时钟RMll-CLK (125M) 三分频后得到的时钟RRAM-CLK(41.66MHz),这样,后端再通过一个24bit转8bit模块即可将数据进行实时传输。

图5 24bit转8bit模块

如图5所示,通过RRAM-CLK(41.66MHz)时钟从RAM 中读出一个像素的数据,然后再通过3个RMIl-CLK(125M)传输给千兆网,即做了一个实时的并串转化。如此流水 *** 作下去,当从RAM 中读完640个像素时,千兆网控制模块将停止读RAM *** 作,等待下一行数据的到来。当DVI解码后的下一行数据一旦往RAM 中存储的时候(至少已经往其中存储了1个像素),千兆网控制模块又开始从RAM 中读取数据,如此循环,直到第1024行数据的640个像素数据被传输完。

在这里,实时传输具有如下特点:(1)往RAM中存数据和从RAM 中取数据同时进行;(2)存RAM 的速度快,读RAM 的速度慢;(3)对写RAM *** 作,先把规定的数据存完,用时为t ,然后进入等待阶段 (t=t1-t2为行周期);对读RAM *** 作,把存好数通过 的时间传输出去,必须满足t3

标准的分辨率1280 X 1024,刷新频率为60Hz的行时钟为64KHz,周期为t=15.625微秒;而从RAM 中读完半行像素(640个)数据的时间是:t3=(1/41.66MHz)X640=15.36微秒。显然,在一个行周期里,只往外传出半行的数据,传输时间差t-t3=265ns>0,且该时间差满足千兆网传输所必需数据包间隔。由于写RAM 的时钟(108MHz)比读RAM 的时钟(41.66MHz)快得多,所以在写RAM 的同时可以对RAM 进行读 *** 作(至少已经往RAM 存储了1个像素),边写边读,实现了视频数据的实时传输。同理,另外一路的千兆网设计与此相同。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)