设计人员时常需要通过增加计算能力或额外输入(或两者)延长现有的嵌入式系统的寿命。而可编程系统平台在这里大有用武之地。我们曾经希望用安全网络连接功能升级一套网络可编程系统。安全网络连接功能需要加密才能运行安全外壳 (SSH)、传输层安全 (TLS)、安全套接层(SSL) 或虚拟专用网 (VPN) 等协议。这种安全需求与把各种系统接入因特网的需求同步增长,例如,为了启用远程管理与分布式控制系统。

协处理硬件可编程系统基本上是一个或几个CPU( 运行 *** 作系统与应用软件)的组合,外加一个 FPGA。FPGA 在其中用作灵活的接口“适配器”及协处理硬件。我们可以在单独辅助芯片上实现可编程系统,或者将全部都集成到单个的器件上。我们可以根据 FPGA 器件和 CPU 之间的通信方式,采用不同方法调节系统性能和功能。

其中一种方法就是添加对等处理器,通过内存映射状态和控制寄存器与 CPU实现同步。因为通过同一系统总线运行所有通信会很快降低性能,因此我们实际上希望把 CPU 数据流与对等处理器分开。而采用赛灵思 Central DMA 或多端口储存器控制器 (MPMC) 等片上系统组件能够轻松满足上述愿望。

另外,也可以增加一个协处理器,这种情况下能通过增加自定义指令(也叫编译功能)有效地扩展 CPU 的指令集。例如,它适合浮点单元,而且赛灵思结构协处理器模块 (FCM) 技术能轻松支持上述功能。此处的优势是在 CPU 和协处理器之间使用一条从内存到系统总线的专用通信通道。对于 PowerPC,其为辅助处理单元 (APU),而对于 MicroBlaze,则是快速单工链路 (FSL)。

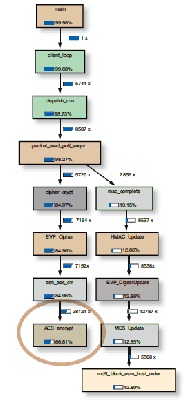

图 1 — 在采用 Valgrind 工具的 SCP 传输中,AES 加密占用三分之二的计算任务。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)