RapidIO总线的出现及其体系结构和应用

传统总线多采用并线总线的工作方式,这类总线一般分为三组:数据线,地址线和控制线。实现此类总线互连的器件所需引脚数较多,例如对于64位数据宽的总线,一般由64根数据线,32-40根地址线以及30根左右的控制线,另外由于半导体制造工艺的限制还要加上一定数量的电源引线和地线,总共会有约200根左右的引线,这给器件封装、测试、焊接都带来了一些问题,如果要将这种总线用于系统之间的通过背板的互连,由此带来的困难就可想而知。并线总线的另一个问题是时钟与信号的偏移容限的问题,对于这样一组并行信号线的集合,信号的采样是取决于时钟信号的上升沿或是下降沿,这样对于信号的跳变和时钟的跳变时刻的时间差就有一个上限值,随着速率的升高,布线长度、器件门电路自身的翻转时间都会影响总线的速率。

用于处理器之间互连以及背板互连的另一个主要技术是以太网,近些年来,以太网在存储、电信、通讯、无线、工业应用以及嵌入式应用中得到大量的应用,现有的成熟的硬件和协议栈降低了开发的复杂性和产品的开发成本。但是在局域网和广域网中得到很好应用的以太网用于这种芯片级或是板极的系统互连显示出了低效率、高延时的特性,QOS需要高层软件的参与,造成软件模块化结构不清晰。尤其是当背板的传输速率从1Gbps增加到10Gbps时,增加的处理要求已经超出了以太网的能力。

RapidIO技术最初是由Freescale和Mercury共同研发的一项互连技术,其研发初衷是作为处理器的前端总线,用于处理器之间的互连,但在标准制定之初,其创建者就意识到了RapidIO还可以做为系统级互连的高效前端总线而使用。1999年完成第一个标准的制定,2003年5月,Mercury Computer Systems公司首次推出使用Rapid IO技术的多处理器系统ImpactRT 3100, 表明RapidIO已由一个标准制定阶段进展到产品阶段,到目前为止,RapidIO已经成为电信,通迅以及嵌入式系统内的芯片与芯片之间,板与板之间的背板互连技术的生力军。

RapidIO是针对嵌入式系统的独特互连需求而提出的,那么我们首先来说明嵌入式系统互连的一些基本需求:嵌入式系统需要的是一种标准化的互连设计,要满足以下几个基本的特点:高效率、低系统成本,点对点或是点对多点的通信,支持DMA *** 作,支持消息传递模式交换数据,支持分散处理和多主控系统,支持多种拓朴结构;另外,高稳定性和QOS也是选择嵌入式系统总线的基本原则。而这些恰是RapidIO期望满足的方向。所以RapidIO在制定之初即确定了以下几个基本原则:一是轻量型的传输协议,使协议尽量简单;二是对软件的制约要少,层次结构清晰;三是专注于机箱内部芯片与芯片之间,板与板之间的互连。

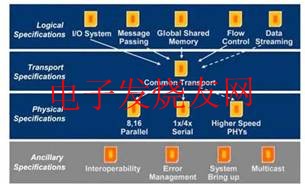

RapidIO采用三层分级的体系结构,分级结构图如下图所示:

图1:RapidIO三层分级体系结构图

由此图可见,RapidIO协议由逻辑层、传输层和物理层构成。最明显的一个特点就是RapidIO采用了单一的公用传输层规范来相容、会聚不同的逻辑层和物理层,单一的逻辑层实体增强了RapidIO的适应性。物理层定义了串行和并行两个实体,得到广泛应用的只有串行方式,尤其是用在背板互连的场合,串行方式可以在两个连接器之间允许80-100cm的连线,单链路传输带宽可达10Gbps。目前RapidIO的标准是Version1.3,在未来的Version2.0规范中定义了更高的传输速率,可以得到更高的传输带宽。

目前,RapidIO在无线基站系统中已经得到了广泛的应用,同样在视频处理,语音处理,高性能计算机及存储领域也会得到越来越多的应用。在实现芯片到芯片之间、板与板之间的高速互连上,RapidIO所能带来的好处也越来越直观,对于简化系统设计、高带宽、低延时等特点也被开发人员广泛接受。下一代的RapidIO在应用上也要向机箱与机箱间的高速互连方向上发展,同时也会提供更高的传输速率,2.0规范中已经可以实现40Gbps的带宽。我们相信,随着越来越多的处理器支持RapidIO接口,RapidIO的应用前景会越来越光明

RapidIO信号完整性测试及其最必要的波形参数测试

众所周知,当今世界数字技术飞速发展,无论您是一位从事电信产品或是数据通信产品,PC,服务器及相关产品,高速半导体集成电路设计,或是高速光电收发模块,高速信号处理,高速互连器件(诸如高速接插件,高速数字传输电缆)等领域的研发及测试工程师都会面临着一个共同的挑战——Signal Integrity(SI)——信号完整性。

大概10年前我们所提到的数字产品,其时钟或数据频率大多在几十兆之内,信号的上升时间大多在几个纳秒,甚至几十纳秒以上。那时的数字化产品设计工程师进行的就是“数字设计”――只要掌握布尔代数等数字方面的诸多知识,保证逻辑正确,就能设计出其所期望的性能的产品。而现在的数字技术已经发展到几千兆,甚至几十千兆的传输速率,信号的上升时间大多在一纳秒以内,诸如串扰,阻抗匹配,EMI(电磁兼容),抖动等射频微波领域才会遇到的问题,如今变成了高速数字设计必须解决的关键性问题。这就要求我们的工程师不但要具备数字方面的设计知识,同时也要具备射频微波方面的设计知识;不但要掌握时域及逻辑域的测量技术,还要掌握频域的测量技术。

高速数字设计与测试在欧美,日本等技术先进国家近些年来已成为一个非常热门的行业,它是实现高性能数字化产品的基础,就如同一个城市的道路建设,只有路修得好,车才能跑得既稳又快。因此,国内外很多大公司都相继成立了高速数字设计与测试(信号完整性分析)的研发力量。

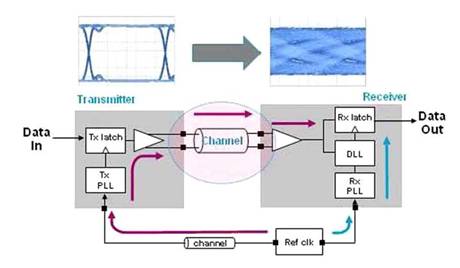

图2:典型的高速互连系统

图2是一个典型的高速互连系统,包括:发送器,传输通道和接收器。针对这种高速互

连系统(如RapidIO互连系统)的信号完整性测试分析,我们需要考虑三个方面:

1、 信号波形参数测试分析:一般用示波器测试分析发送端的信号或接收端的信号,通

过眼图/模板、抖动等参数的测试分析决定是否满足规范或设计要求。

2、 互连测试分析:这是从引发波形失真的源头去测试,测试通道的差分阻抗,衰减等

参数,分析是否会引发信号完整性问题。

3、 接收性能测试:只是信号波形好不能保证整个系统误码率一定很低,系统一定稳定

和可靠,因为接收性能的好坏也是决定系统性能和稳定性的一个关键方面。

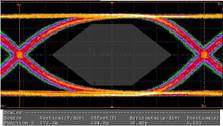

首先我们需要考虑的是信号波形参数测试分析部分。信号波形参数测试分析一方面检测被测系统是否满足规范或设计的要求,另一方面是帮助我们找到问题的根源。图3是安捷伦信号波形参数分析解决方案。DSA90000A数字信号分析仪带宽从2.5GHz到13GHz可选和带宽可升级,采样速率每通道高达40GSa/s,存储深度最深每通道达1GB。DSO9000A带宽从1GHz到4GHz可选和带宽可升级,采用速率最高达20GSa/s,存储深度最深达1GB(两通道使用下每通道指标),卓越的性能满足RapidIO测试的要求。

注:测试3.125Gbps的RapidIO需要8GHz带宽,测试2.5Gbps的RapidIO需要6GHz

带宽,测试1.25GHz的RapidIO需要4GHz的带宽。

图3:安捷伦信号波形参数分析解决方案DSA90000A和DSO9000A

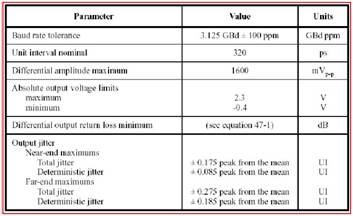

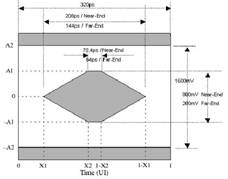

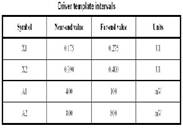

针对串行RapidIO,信号波形参数测试内容如下(以3.125G为例):

表1:串行RapidIO信号品质测试规范(以3.125Gbps为例)

图4:串行RapidIO模板定义

图5:串行RapidIO测试结果示例(使用安捷伦基于示波器的自动测试软件)

RapidIO互连通道测试

物理层结构正日益成为高速数字系统性能的瓶颈。在较低的信号速率时,这些互连的电

长度很短,驱动器和接收机一般是导致信号完整性问题的最主要因素。但随着时钟速率、总

线速率及链路速率突破每秒千兆大关,物理层特性测试正变得日益关键。

时域分析一般用来描述这些物理层结构的特征,但通常情况下,设计人员在测试时往往

只考虑器件工作在其被期望的工作模式上时的情况。为了获得一个完整的时域信息,必须要

测试反射和传输(TDR和TDT)中的阶跃和脉冲相应。

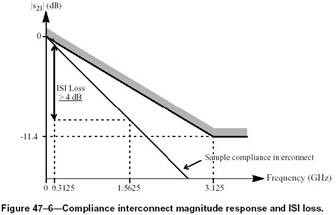

为了全面描述物理层结构的特征,还必须进行频域分析。S参数模型说明了这些数字电

路结构所展示出来的模拟特点包括:不连续点反射、频率相关损耗、串扰和EMI等性能。

为使设备性能符合标准,眼图增加了重要的统计分析功能。为利用全面特性检定技术改

善仿真能力,可以采用基于测试结果的S参数或RLCG模型提取技术。

随着在多种工作模式下进行数字和模拟综合分析(时域和频域)变得越来越重要,要完

成这些测试功能,通常需要使用多种测试仪表,同时 *** 作多种仪表正变得越来越困难。物理

层测试系统PLTS是为了解决这种困难而设计的。它使用已获专利的变换算法,自动地在频

域和时域里表示在所有可能的工作模式(单端、差分、共模和模式转换)下所得到的前向和

后向、传输和反射的测试数据。强大的虚拟码型发生器功能可以把用户定义的二进制序列应

用到被测的数据上,形成仿真的眼图。同时,可以提取高精度的RLCG模型,用来提高建

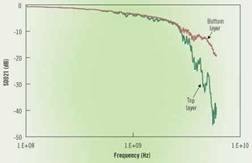

模的仿真的精度。图6是RapidIO互连通道测试要求:

图6:串行RapidIO互连通道损耗规范(以3.125Gbps为例)

图7:串行RapidIO互连通道测试结果(使用Agilent物理层测试系统)

安捷伦物理层测试方案功能

1、 高速互连的时域分析:可以得出16个单端时域参数;可以得出16个混合模式(或差

分模式)时域参数。

2、 高速互连的频域分析:可以得出16个单端频域参数;可以得出16个混合模式(或

差分模式)频域参数。

3、 支持校准引导和多种校准模式,如:TRL,SOLT,夹具直通校准方法等。

4、 基于测量结果的眼图仿真:用户定义虚拟码型,进行眼图仿真。产生眼图后,可以

用光标或自动进行测量,如:模板,抖动,眼图张开,上升时间和下降时间等。

5、 支持频域S参数模型和时域RLGC模型提取,可以导到建模和仿真软件中,进行更

复杂的仿真分析。

图8:安捷伦物理层测试系统

RapidIO接收性能和误码率测试

接收性能测试往往被忽视。对于低速系统,一般没问题,但当信号速率上升到了2.5Gbps

上后,规范对接收性能就有比较严格的要求。

一旦我们测试出了接收的性能或接收的模板,我们就可以知道我们的信号完整性设计应

该设计到什么程度。比如,接收性能非常好,则信号波形较差,整个系统也仍然会稳定和可

靠。

接收性能测试需要这样一台仪器:

1、 一台高性能误码仪:能够发抖动非常小,波形非常好的信号;能够接收信号和分析

误码率。

2、 能够发带抖动的信号,并且抖动是经过校准的,设置输出多大抖动,实际就是多大

抖动,误差较小。

3、 具备多种抖动产生能力:正弦波抖动SJ,周期性抖动PJ,码间干扰抖动ISI,随机

抖动RJ,边带不相关抖动BUJ等。

RapidIO抖动容忍度的测试要求:

. pk-pk Receiver Jitter Tolerance =208ps (0.65UI)

. Jitter includes 3 components : Rj,Dj, Sinusoidal Jitter

. DJ tolerance shall be at least 118.4ps (0.37 UIp-p) .

. Tolerate an addiTIonal sinusoidal jitter with any frequency and amplitude

defined by the Far mask

图9:RapidIO抖动容忍度测试要求

安捷伦接收性能测试方案功能

安捷伦公司的N4903A/B J-BERT是典型的接收性能测试仪器。图13是J-BERT总览。

图10:安捷伦接收性能测试方案J- BERT总览

JBERT实现功能:

1、接收性能测试

2、误码率测量

3、快速眼图和模板测试

4、码型捕获

5、抖动容忍度测试

RapidIO协议层调试

RapidIO协议层分析和调试也是设计RapidIO系统时需要考虑的部分,尤其对于RapidIO

软件设计者来说。RapidIO协议分析仪可以帮助我们完成RapidIO协议部分的测试和调试。

方案功能如下:

1、捕获和分析串行RapidIO和PCI-Express协议

2、支持包头识别和触发

3、提供包级数据滤波

4、支持调试物理层,传输层和逻辑层

图11:串行RapidIO和PCI-Express综合协议分析仪

简短小结

RapidIO互连技术已经在各种无线通讯、雷达信号处理、高性能嵌入式处理等场合大量

使用,针对RapidIO设计的复杂性,安捷伦开发了全套的设计和测试解决方案:用ADS来

进行系统的仿真和设计,用示波器进行波形参数的测试分析,用物理层测试系统进行互连通

道的测试和分析,用抖动误码仪进行系统误码率和接收灵敏度的测试和分析,用协议分析仪

进行协议层的分析和调试,以帮助研发工程师最快的开发RapidIO系统。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)