脉冲压缩技术是指对雷达发射的宽脉冲信号进行调制(如线性调频、非线性调频、相位编码),并在接收端对回波宽脉冲信号进行脉冲压缩处理后得到窄脉冲的实现过程。脉冲压缩有效地解决了雷达作用距离与距离分辨率之间的矛盾,可以在保证雷达在一定作用距离下提高距离分辨率。

线性调频信号的脉冲压缩

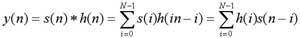

脉冲压缩的过程是通过对接收信号s(t)与匹配滤波器的脉冲响应h(t)求卷积的方法实现的。而处理数字信号时,脉压过程是通过对回波序列s(n)与匹配滤波器的脉冲响应序列h(n)求卷积来实现的。匹配滤波器的输出为:

(1)

(1)

依据式(1)的实现方法叫做时域相关法。根据傅里叶变换理论,时域卷积等效于频域相乘,因此,式(1)可以采用快速傅里叶变换(FFT)及反变换(IFFT)在频域内实现,称为频域快速卷积法。

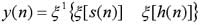

用频域方法实现数字脉压,其基本原理是先对外部采样信号进行快速傅里叶变换(FFT)以求得回波信号频谱S(w),再将S(w)与匹配滤波器频谱H(w)进行乘积运算,最后对乘积结果进行快速傅里叶逆变换(IFFT)得到脉压结果Y(n),用公式表示为

(2)

(2)

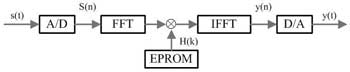

频域快速卷积法的原理如图1所示,存储器中存储的是匹配滤波器传递函数H(k)。

图1 频域脉冲压缩原理框图

依据匹配滤波理论,数字匹配滤波器的脉冲响应h(n)及传递函数H(k)为

h(n)=s1(-n),H(k)=s1(k) (3)

其中, s(n)为雷达发射信号序列;S(k)为信号序列频谱。

数字脉冲压缩系统

1 系统构成和硬件设计

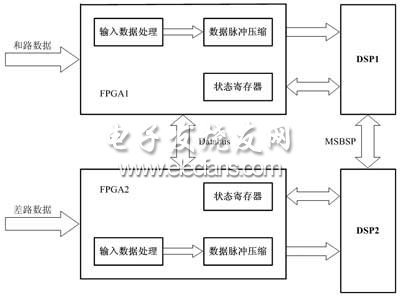

本系统是单脉冲雷达信号处理机的一部分,由于单脉冲雷达所需要处理的距离、方位/俯仰两路信号来自同一发射信号源的目标反射回波,要求对两路信号进行同时、同频ADC采样和完全相同算法的脉冲压缩处理。针对这一特点,雷达数字脉冲压缩系统将相同的脉冲压缩处理功能移至两片FPGA芯片内。由于对雷达体积、重量、功耗等指标有特殊要求,本系统采用二个通道的脉冲压缩处理硬件结构,即方位和俯仰两路信号分时共用一个脉冲压缩通道。雷达信号处理分系统硬件结构如图2所示。

图2 雷达信号处理分机硬件结构图

系统中,数据采样后分为和路和差路(包括航向差和俯仰差)两组数据,分别输入两片FPGA单独进行脉冲压缩计算,脉冲压缩后再送入后端的DSP做谱分析,以确定目标的距离、速度、方位等情况。由框图中我们看到,FPGA不仅要对数据做脉冲压缩计算,还承担了对输入数据处理和读写状态寄存器的任务。状态寄存器存储了脉冲压缩计算的控制参数,由后端的DSP根据分析的结果对其做相应的控制。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)