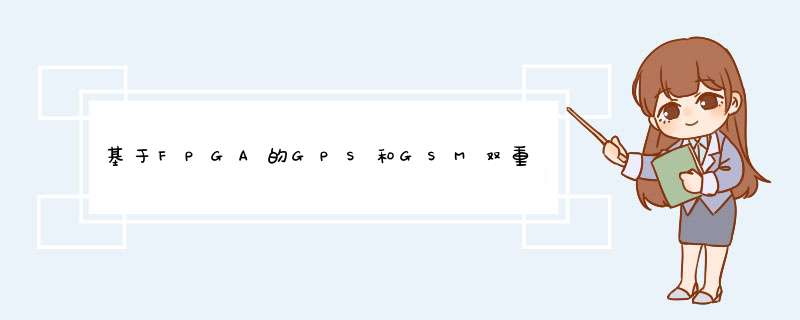

目前在车辆GPS导航系统中,主要是直接利用无差分、无SA误差的GPS定位数据来实现车辆在地图上的定位。考虑到定位信号存在一定的误差,5%概率下误差会超过15 m,同时城市中建筑物、桥梁以及树木等还对GPS信号形成遮挡,甚至会导致信号失效,从而进一步影响定位精度。而车在行进过程中进行导航时,尤其是在路口以及立交桥等特殊地点的导航时,系统往往需要更为精确的定位。为此,本设计充分利用了FPGA强大的逻辑控制功能和NiosⅡ处理器的多可配置标准外设接口功能,结合GPS和GSM功能模块,设计了一款双重定位系统。通常情况下用GPS进行定位,在特殊情况下可以开通GSM网络定位功能实现双定位,再通过GSM网络将定位信息、时间和终端特殊信息传送到监控中心,或者接收监控中心传来的信息,完成定位和监控等功能。

图1 GPS/GSM车载定位系统示意图

1 NiosⅡ软核嵌入式处理器

NiosⅡ处理器是Altera公司的第二代用户可配置的通用32位RISC软核微处理器,是Altera公司特有的基于通用FPGA架构的软CPU内核。N-iosⅡ系列支持使用专用指令。专用指令是用户增加的硬件模块,它增加了算术逻辑单元(ALU)。用户能为系统中使用的每个NiosⅡ处理器创建多达256个专用指令,这使得设计者能够细致地调整系统硬件以满足性能目标。专用指令逻辑和本身NiosⅡ指令相同,能够从多达两个源寄存器取值,可选择将结果写回目标寄存器。同时,NiosⅡ系列支持60多个外设选项,开发者能够选择合适的外设,获得最合适的处理器、外设和接口组合,而不必支付根本不使用的硅片功能。在FPGA中使用软核处理器比硬核的优势在于,硬核实现没有灵活性,通常无法使用最新的技术。随着系统日益先进,基于标准处理器的方案会被淘汰,而基于NiosⅡ处理器的方案是基于HDL源码构建的,能够修改以满足新的系统需求,避免了被淘汰的命运。将处理器实现为HDL的IP核,开发者能够完全定制CPU和外设,获得恰好满足需求的处理器。

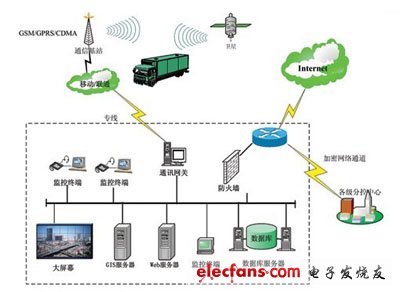

2 系统的硬件设计与实现

定位终端系统的硬件由一块FPGA芯片和GPS模块,GSM模块,外部存储SDRAM,FLASH,SRAM,LCD及控制模块等组成,其结构框图如图所示。FPGA芯片主要实现NiosⅡ软核处理器、片上存储器和各种接口驱动等功能,其包括NiosⅡ系统和外设两部分。NiosⅡ系统包括NiosⅡ处理器、存储器、定时器、串行接口、并行接口和连接各个组件的Avalon交换结构总线。其中GPS_UART和GSM_UART分别实现与GPS和GSM模块的串行通信,LCD控制器实现与人机交互模块的连接。

图2 车载导航系统的硬件结构框图

2.1 GPS和GSM模块

对于GPS模块,采用Zarlink公司的GP2015,它的主要任务是对接收到的GPS信号进行外差式下变频,内部包括一个片内频率合成器、三级混频器、自动增益控制电路及量化器。在其内部使用锁相环频率合成器合成本地参考信号,然后和接收信号进行混频。在该系统设计中,射频前端GP2015需要两个外部时钟,一个是10 MHz的基准频率,另一个是其内部A/D的采样时钟,频率为5.714 MHz;在GPS接收机的设计中,射频前端与基带处理模块的时钟相位保持一致或相位误差比较小时,有助于提高接收机的定位精度。考虑到这一点,在本设计中FPGA和射频前端共用一个时钟源,给FPGA提供一个40 MHz的基准频率,FPGA经过内部的锁相环提供10 MHz和5.714 MHz的时钟信号给射频前端,保证了前端和基带处理时钟的同源。在GP2015内部还集成了一个两位A/D转换器,模拟中频输入为4.309 MHz,输出两位的数字中频信号,频率为1.405 MHz。GSM模块采用Siemens公司的TC35,该型号的GSM模块工作在EGSM 900 MHz和GSM1 800 MHz频率波段,提供话音和数据传输的无线连接,使用40引脚的零插力连接器作为控制数据、话音信号和电源线的应用接口。其串口通信波特率在300 b/s~115 Kb/s之间可选,也可以在1 200 b/s~115 Kb/s之间的8种波特率间自动适配。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)