1 引言

电荷耦合器CCD具有尺寸小、精度高、功耗低、寿命长、测量精度高等优点,在图像传感和非接触测量领域得到了广泛应用。由于CCD芯片的转换效率、信噪比等光电特性只有在合适的时序驱动下才能达到器件工艺设计所要求的最佳值,以及稳定的输出信号,因此驱动时序的设计是应用的关键问题之一。通用CCD驱动设计有4种实现方式:EPROM驱动法;IC驱动法;单片机驱动法以及可编程逻辑器件(PLD)驱动法。

基于FPGA设计的驱动电路是可再编程的,与传统的方法相比,其优点是集成度高、速度快、可靠性好。若要改变驱动电路的时序,增减某些功能,仅需要对器件重新编程即可,在不改变任何硬件的情况下,即可实现驱动电路的更新换代。

2 CD 1501D CCD工作参数及时序分析

2.1 TCDl50lD CCD工作参数

所选器件是日本TOSHIBA公司的TCDl50lD CCD作为光电传感器,该芯片是高灵敏度、低噪声和宽动态范围的线阵CCD器件。主要参数如下:

光敏像元数:5000个 像元尺寸:7μm×7μm×7μm

光谱响应范围:300~l 000 nm灵敏度:10.4~15.6V/Lx.s

动态范同典型值:3 000 nm饱和曝光度典型值:0.23Lx.s

驱动时钟频率最大值:12 MHz

该器件正常工作的驱动脉冲主要有:复位时钟RS、移位脉冲φ1、φ2和转移脉冲SH。该器件具有5 000个有效像元,正常工作还需要76个虚设单元输出(dummy outputs)信号。由于该器件是两列并行传输,所以在一个周期内至少需要2538个φ1(或φ2)时钟脉冲才能完成一帧图像转移。

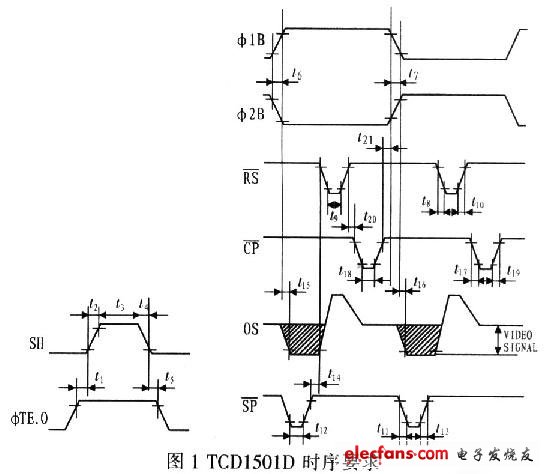

2.2 驱动时序分析

各驱动时序之间正确的先后关系是保证CCD正常工作的前提。具体时序关系如图1所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)