所用器件: Kintex7-325T,-3速度等级,商业档

系统描述: 使用3个HPbank接了4片16位宽的DDR3颗粒,DDR3控制器使用MIG生成,Data Rate 为1866Mbps。使用的是NaTIve Interface,命令和数据通道分开,分别提供一读一写2个数据通道。

现象描述:在做高温测试时,在芯片结温超过110°C之后(芯片结温可以用JTAG实时监测),整个系统开始不正常。此时通过FPGA内部添加ILA逻辑分析仪进行分析,发现DDR3控制器的读通道开始没有响应,即发送读命令下去,但是并没有数据返回,看起来像是DDR3控制器已经跑死了。

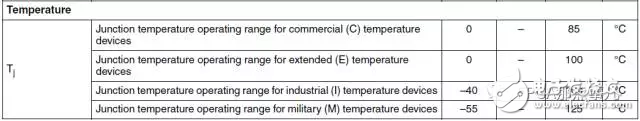

同样从Xilinx器件本身来说,商业档的芯片,手册标称的温度范围是0-85℃,即使是-E等级的芯片,标称也不过是0-100℃。

从测试现象来说,DDR3控制器在110℃以后才出问题,其实已经超过了普通商业档芯片的标称工作范围。但凡事无绝对,本着同之前LVDS的Case一样的态度,尝试一下,没准我们能发现一些更深层次的问题呢!

分析过程:因为现在没什么头绪,我们就从一些最常规的手段去尝试。

1. 降频

客户的系统对DDR3贷款的需求比较大,最多降到1600Mbps,降得再低可能系统带宽无法保证。在1600Mbps时,温度特性没有什么明显差异,也是在110°C左右开始出现问题。

2. 单独测试DDR3读写

使用MIG生成独立的DDR3读写测试工程,发现此时即使结温升到120℃,DDR3的读写逻辑依旧工作正常。这说明PCB layout和信号完整性应该没有太大的问题。难道问题出现在TIming上?

3.TIming时序

仔细重新梳理了一遍设计,和时序约束,该约束的都约束上了,而且从最终的实现报告上来看,所有的时序都满足要求,没有违例。

应该也不是TIming约束的问题。

至此我们排查了逻辑设计,Timing约束和报告,PCB layout,没有发现特别的疑点。那么还有那些因素可能影响呢,会不会是电源问题呢?

4. 电源

在整个系统正常跑起来后,用示波器接在电源上进行分析。在常温下,几路电源都完全工作正常。随着温度的升高,到约110℃附近,FPGA的核压Vccint的那一路电源,1.0V会有一个明显的下降。

会不会是1.0V的电源供电不足导致的,因为随着温度的升高,FPGA的功耗也会显著的加大。

解决办法:

使用外部的独立稳压电源给1.0V单独供电,再进行高低温测试,即使结温升到120℃,系统仍然工作正常。看起来正是电源的问题。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)