此过程主要是用软件来仿真你的设计,看看结果是否符合你的设计要求

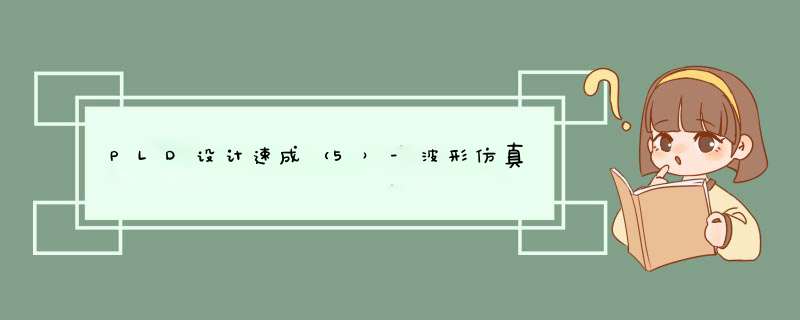

编译好以后,打开波形编辑器,MAX PLUSII->Waveform Editor

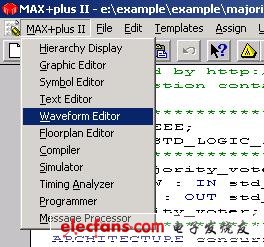

载入端口,Node->Enter Nodes from SNF

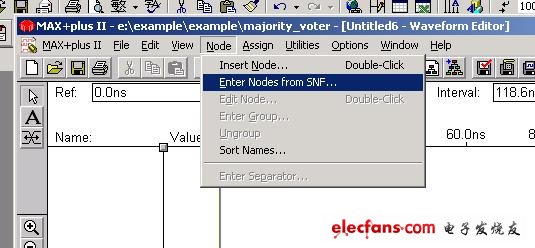

将d出下面窗口,你按下面步骤 *** 作:

点List,将出现端口列表,你默认是选择全部,你也可以通过左键和Ctrl组合来选择你想要的信号。

点=>将你的信号加入SNF文件中

点OK

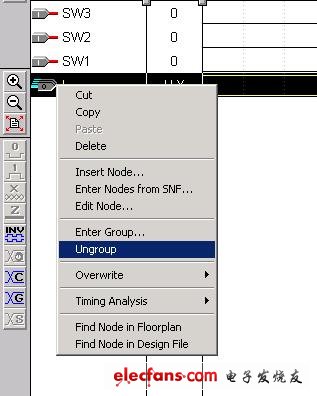

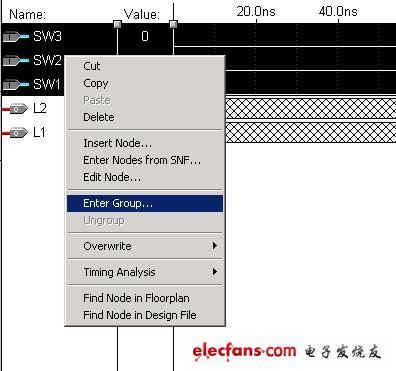

为了方便观察,我们把信号展开

如果需要再次合并可以按住SHIFT键,用鼠标左键选上要合并的信号,再点右键->Enter Group

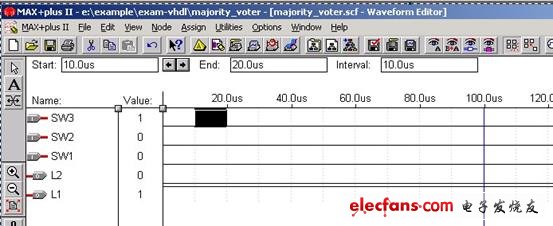

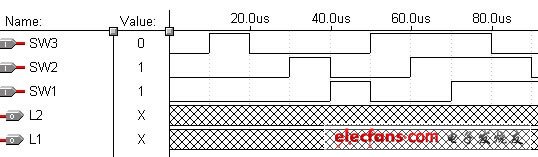

下面我们将对信号进行赋值,首先选中一个要赋值的信号区间,如SW3的10us到20us范围,按住鼠标左键,在SW3的10us到20us的范围只能够那拉出一个黑色区域,松开鼠标左键,再点左边工具栏上的“1”,使这个时间段,SW3就被赋值为高电平,如下图:

(注意时间不要选择太小,比如就选10ns,这样结果可能不对,因为电路的延迟可能就达到10ns)

你将其他信号按你希望的加上激励

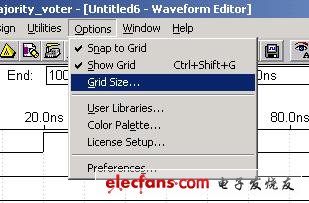

在上面过程中,你可能要遇到下面设置:

Snap to Grid:鼠标按网格选取,用鼠标左键可以决定是否选取

Show Grid:显示网格

Gride Size:设置网格大小(这个非常有用,在你一些设计中经常要改变网格大小,便于你选择)

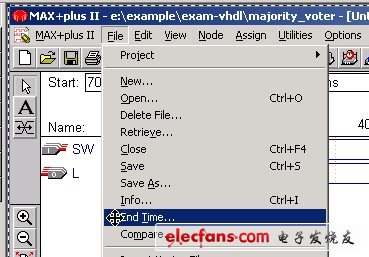

End TIme:设置仿真结束时间(这个在设计中也经常用到,否则默认的仿真时间只有1us)

下面是加激励后的波形(end TIme =200us,gride size=10us)

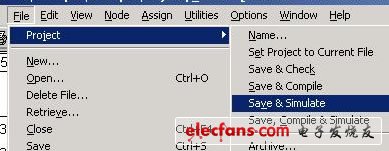

点FILE->PROJECT->save&simulate

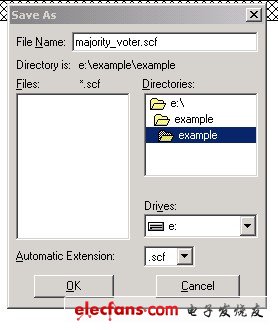

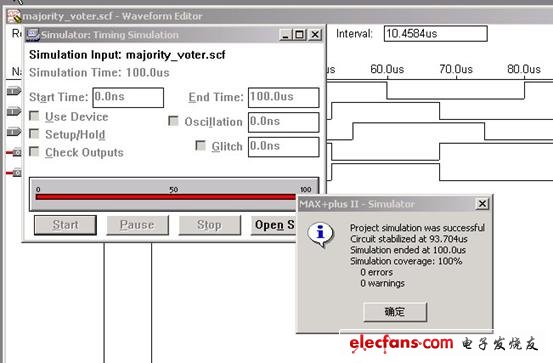

这时会d出保存窗口,我们保存为majority_voter.scf

点OK,将会防真,如果正确会d出窗口(图)

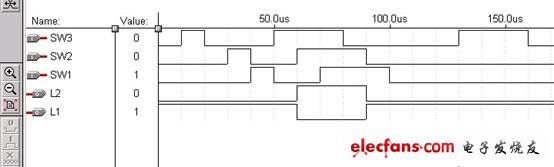

点确认,再点open SCF,将出现防真后的波形

波形图显示的逻辑功能和设计目的完全一样,这样我们就可以把程序在线下载到芯片EPM7128SLC84-15中。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)