由LCD液晶显示器制作的显示面板广泛应用于军用设备中,本设计采用Spartan-3E FPGA为硬件,该2×16字符型LCD内嵌一个Sitronix ST7066U图形控制器,实现了LCD显示器的字符或者汉字的满屏显示、满屏移动显示以及单个字符在屏幕上的移动显示,所有功能用VHDL语言实现,符合LCD显示器要求,达到各种显示效果。

由于LCD 液晶显示器体积小、重量轻、功耗低,应用非常广泛,如作为飞机、坦克和船上的显示面板,可缩小原CRT显示器的所占空间,减轻设备重量,增强机动性。

本设计采用Spartan-3E开发板上的一个内嵌Si.tronix ST7066U图形控制器的字符型LCD,实现了:(1) 单个字符在任意位置的显示以及字符的满屏显示及满屏移动显示;(2) 自定义字符(汉字)的显示以及单个字符的满屏移动显示。其中,图形控制器[1]负责接收控制指令及数据并将其发送给LCD显示器。

1 Sitronix ST7066U 图形控制器

该控制器有三个内部存储空间,DD RAM、CGROM、CG RAM,送数据之前应先初始化。

(1)DD RAM(显示数据RAM)

存储字符编码,从物理上讲DD RAM共有80个字符位置,每行有40个字符,但只有16个可被显示,剩余的24个不被显示。在读或写之前,需初始化地址计数器,地址计数器在读或写之后可保持常数或者自动增1或减1。

(2)CG ROM(字符产生器ROM)

包含每个事先定好的字符的字体位图。

(3)CG RAM(字符产生器RAM)

包含8位的自定义字符位图,每个自定义字符位由8行位图的5个点组成,具体用法与DD RAM相同。

1.1 与FPGA 的接口信号

LCD与FPGA的接口信号[2]有:(1)使能信号LCD_E;(2)寄存器选择信号LCD_RS;(3)读/写控制信号LCD_RW;(4)4根LCD数据线与StrataFlash数据线SF_D《11:8》复用。

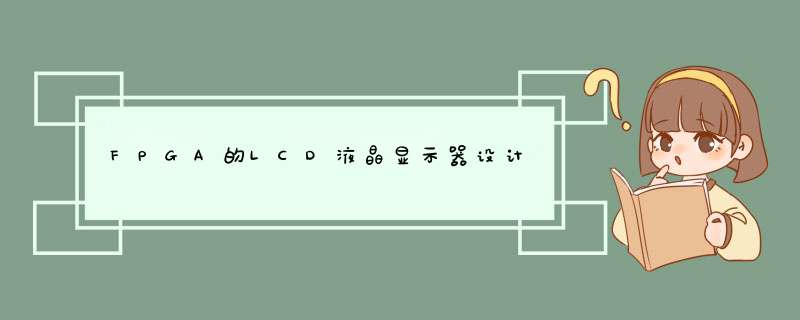

1.2 时序分析

SF_D《11:8》的数据值,LCD_RS、LCD_RW必须建立并在LCD_E 转向高电平之前至少稳定40 ns,LCD_E 保留高电平时间至少230 ns。在许多应用中,LCD_RW恒置低,因为一般不会从显示屏读取数据。

如图1所示,数据以8位形式传送,分为高4位和低4位,先传高4位再传低4位,其间隔时间至少1us。一个8位的写 *** 作在下个通信之前间隔时间至少为40 us,而在清屏命令之后该延时需增至1.64 ms。

图1 字符型LCD 接口时序图

2 数据显示设计

2.1 流程图

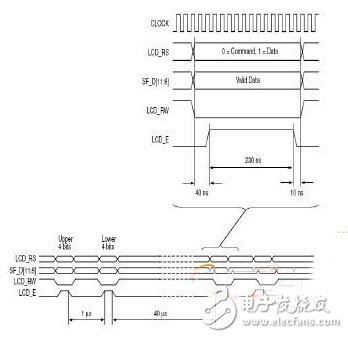

如图2所示,LCD数据显示包括上电初始化、配置显示屏、写数据给显示屏,在写数据之前应先设定初始地址。

图2 LCD 显示流程图

本开发板晶振为50 MHz。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)