本文研究的内容就是一种在实际项目中应用的晶闸管阀组的触发电路设计。

1 触发电路设计

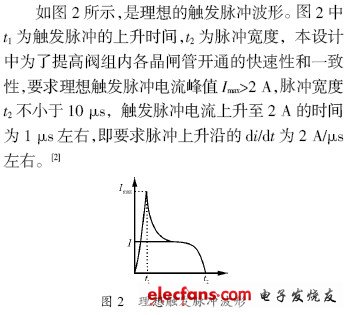

触发脉冲电流的上升沿时间越短、峰值越大,晶闸管开通扩散的速度就越快,当所有晶闸管开通时间都大大缩短后,晶闸管之间开通的相对一致性就大大提高,从而降低了串联阀中个别晶闸管长时间承受过高电压而损坏的几率。

1.1 触发电路组成与工作原理

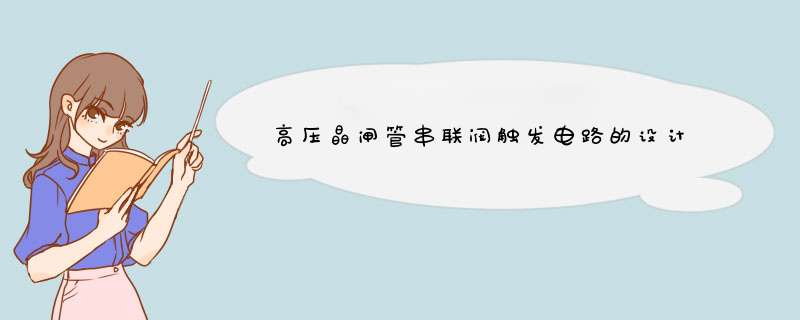

触发电路结构图如图1 所示,主要包括如下几个部分。

1)单相隔离供电变压器T1 变比为AC220/AC220、一次侧与二次侧间绝缘电压35 kV,为脉冲回路提供产生脉冲电流所需的能量。

2)充电限流电阻R3 限制电容C1的充电电流。

3)防反流二极管D0 防止电容C1向变压器T1倒送能量。

4)储能脉冲电容器C1 储存产生脉冲所需的能量,最高充电电压Uc可达310 V。

5)阻容回路部分的R2和C2 起调整脉冲波形形状的作用。

6)脉冲CT 变比20/1,通过脉冲CT 形成最终触发脉冲。

7)放电电阻R1 限制放电电流。

8)非线性电阻R4 其转折电压为400 V,用于保护MOSFET。

9)脉冲信号板用来接收控制器通过光纤发来的脉冲光信号,经过光电转换,驱动MOSFET(IRFP460)开通与关断,使电容C1 受控制器的控制进行放电。脉冲信号板从变压器T1 二次侧取能,通过单相变压器AC220/AC20,经过整流滤波,由7805 和7812 输出稳定的+5 V和+12 V电源,为脉冲信号板提供供电电源。

10)BOD 模块用来保护晶闸管在承受过电压时触发导通,防止晶闸管被高压击穿。

触发电路工作原理:隔离变压器T1 一次侧接AC220 V电源,二次侧通过电阻R3和二极管D0向电容C1充电,当C1上的电压达到峰值AC220 V,即310 V 左右时,二极管反向截止,电容C1 上保持310 V左右的电压。当控制器发出触发脉冲信号,信号经过光纤传导至脉冲信号板,经光电转换后驱动MOSFET 开通,电容C1开始通过电阻R1放电,这样就有瞬间大电流通过8 个接在晶闸管门极的CT,通过CT同时产生8 路晶闸管触发电流信号。[3]

1.2 触发电路的电位

在高压条件下,晶闸管串联阀的绝缘问题是非常重要的一个环节,如果绝缘问题处理不好,那将会严重影响设备运行的安全性与可靠性。

触发电路的高电位部分和低电位部分之间的隔离主要是靠触发CT 和穿过CT 的10 kV 绝缘的电流线,为了降低对触发CT 绝缘等级的要求,减小在高压条件下串联阀主回路对脉冲回路的影响,同时降低对脉冲回路绝缘等级的要求,将变压器T1 二次侧的地直接接在晶闸管串联阀的第4和第5 个晶闸管之间,即串联阀主回路的中点电位,将脉冲回路的电位拉高至1/2 高电位,如图1中标记为中点电位点的地方。从而使整个串联阀结构的电位全部提高,这样,绝缘的要求就加到隔离供电变压器T1 的一次侧和二次侧之间,而这里选用的变压器T1 的一次侧与二次侧绝缘水平达到35 kV,能够很好的满足10 kV 电压等级的要求。这样设计能够大大降低串联阀结构设计当中对绝缘的要求,也降低了对触发电路的绝缘要求。

脉冲信号板的地与变压器T1 一次侧的中点电位点相连,使脉冲信号板的电位也拉到高电平,从而使脉冲信号板能够在高电压下可靠工作。

1.3 触发电路参数对脉冲波形的影响

本设计中使用的晶闸管串联阀是由8 支额定电压6 000 V、额定电流1 000 A 的晶闸管串联压接成的,适用于10 kV电压等级。触发脉冲电流的产生是利用电容充电储能后放电,形成尖峰大电流,再通过接在每个晶闸管门极上的脉冲CT转换为触发脉冲,来驱动晶闸管。影响触发脉冲波形的因素主要有两个方面:一是电容放电回路的寄生电感;二是触发电路电阻、电容的参数配置。这里为了减小电容放电回路的寄生电感,放电回路的电阻采用无感电阻,大电流线走线方式采用往返走线,即大电流线穿过触发CT后再按原路从CT外部折回,这样走线的目的是为了最大限度地减小大电流线所围的面积,以及最大限度地减小回路寄生电感。

触发电路电阻电容参数对触发脉冲波形的影响如下。各参数中对触发波形影响较大的是放电电阻R1、阻容回路电容C2、储能脉冲电容器的最高充电电压Uc。R1阻值越小,脉冲峰值越高,上升沿越陡;阻容回路电容C2 越小,脉冲峰值越小;Uc值越高,脉冲峰值越高,上升沿越陡。阻容回路的工作原理如图1 所示,当电容C1 充电储能后,MOSFET 受控制信号的控制开通,C1 通过电阻R1瞬间放电,阻容回路中的电容C2 瞬间短路,将电阻R2 旁路掉,触发脉冲瞬间上升,之后C1 开始向C2 充电,当C2 充电完毕,电阻R2 接入放电回路中,此时脉冲上升沿结束,脉冲电流开始减小。表1 是实验中所选电路参数与所测得波形参数的对照表。需要说明的是,表1 中的波形上升时间为10%脉冲峰值电流到90%脉冲峰值电流时间。达到2A时间为电流从0耀2 A的时间。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)