随着科技的飞速发展、高分辨率的数模混合电路的应用不断深入,电路设计日趋复杂,精度越来越高,所以高精度AD转换电路的设计就成了仪器仪表及各种测量控制系统的难点。本系统来源于仪器仪表的温控系统设计,采用高精度、低温漂的优质模拟、数字器件,辅以52系列单片机为控制器,以复杂可编程逻辑器件 CPLD (Comp lex Programmable Array Logic)为频率测试的硬件平台,实现了高分辨率、低线性误差的AD转换器的设计。通过本设计掌握高精度、低漂移的高端AD转换器的设计方法, CPLD的设计,以及52系列单片机的硬件设计及软件编程。

1 系统功能及结构

系统主要目的是设计一个16位的VFC式AD转换器,利用积分原理,将输入电压(或电流)转换成频率输出。采用计数频率高的CPLD器件实现测频,单片机控制CPLD的测频 *** 作和频率的计算。

用V /F转换器完成AD转换,需要1个定时器和2路计数器,计数器的计数频率限制了V /F器件输出频率的提高。本设计采用计数频率更高的CPLD器件和单片机共同组成测速模块, CPLD通用性好,避免了对于专用器件的依赖,降低了因专用器件停产或出现供贷问题所带来的风险,同时实现所需的控制。

VFC式AD 转换器脉冲频率与输入电压成比例,其精度高、线性度好、转换速度居中、转换位数与速度可调、与CPU的连线最少,且增加转换位数时不会增加与CPU的连线,因此, VFC为AD 转换技术提供了一种廉价而有效的解决办法。

系统总体可以划分为电压采样部分、模拟- 数字转化部分,控制部分。其中电压采样部分包括:精密测试电压源。模拟- 数字转化部分包括:电压放大和偏置,V /F转换模块,计数转化模块。控制部分包括:控制器模块,键盘,显示模块,系统原理框如图1所示。

为实现各模块的功能,分别选取了较好的方案实现: ①精密基准源,精密低温漂高档基准源,分压;②电压放大及偏置,运算放大器ICL7650; ③V /F转换,采用AD652芯片; ④频率测试,采用CPLD (复杂可编程逻辑器件) ; ⑤控制器,采用凌阳的SPEC061A单片机; ⑥显示,采用液晶屏; ⑦电气隔离,采用光电耦合,所设计的系统如图2所示。

图1 系统原理框图

图2 所设计的系统框图

2 系统硬件设计

2. 1 精密测试基准源

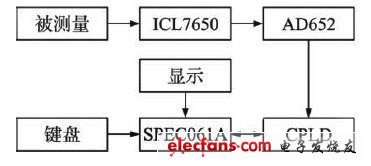

对于16位的AD转换器,满幅度输入电压仅为100 mV,如果要测试它的性能,则需要极高精度和非常低温漂的基准源, 电路原理如图3 所示。

AD586是AD公司高精度5 V的基准电压源,温漂低至2 10 - 6 /℃,噪声为100 nV /Hz,通过固定电阻和可调电阻进行分压产生0 ~100 mV 的电压。为了增加电压的负载能力,须进行电压跟随。OPA333是零漂移精密运放,漂移最大为0. 05μV /℃。同时采用两个2. 5 V的基准源LM336以降低电源波动的影响。LM336 的输出电流为10 mA, 可满足OPA33的需要。分压用的电阻为指针式10 圈可调,可以达到理想的精度。

图3 基准源电路原理图

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)