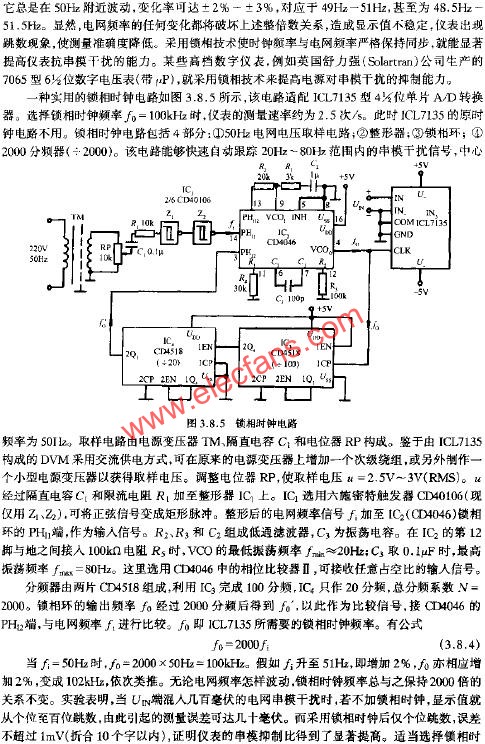

目前广泛使用的3 1/2~5 1/2位数字电压表(DVM),大多选用双积分式或多重积分式单片A/D转换器。其优点是电路简单,抗串模干扰能力强,成本较低。只要设计的时钟频率F0恰好等于50HZ的整倍数,电网串模干扰就被完全抑制掉了。然而电网频率实际上并不稳定,

钟频率,还可配MAX133/MAX134、HI7159型4 3/4~5 1/2位单片A/D转换器使智能数字电压表的电磁兼容性得到改善。

欢迎分享,转载请注明来源:内存溢出

目前广泛使用的3 1/2~5 1/2位数字电压表(DVM),大多选用双积分式或多重积分式单片A/D转换器。其优点是电路简单,抗串模干扰能力强,成本较低。只要设计的时钟频率F0恰好等于50HZ的整倍数,电网串模干扰就被完全抑制掉了。然而电网频率实际上并不稳定,

钟频率,还可配MAX133/MAX134、HI7159型4 3/4~5 1/2位单片A/D转换器使智能数字电压表的电磁兼容性得到改善。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)