当Xilinx 7Series FPGA中,存在3种主要的时钟网络:BUFG,BUFR,BUFIO以及他们所衍生出的各种变种。那么他们有什么主要特点和区别呢?

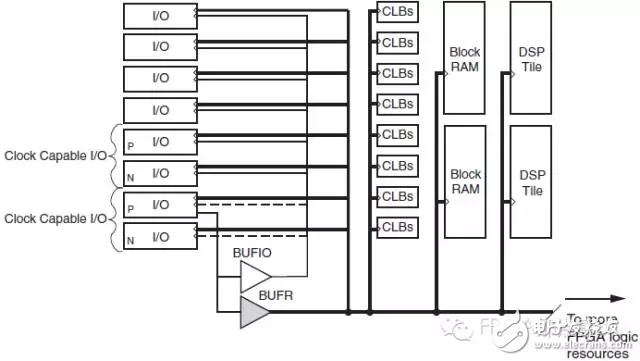

BUFIO是IO时钟网络,顾名思义,它只能驱动IO Block里面的逻辑,不能驱动CLB里面的LUT,REG等逻辑。BUFIO可以被如下节点驱动:

1、SRCCs and MRCCs in the same clockregion

2、MRCCs in an adjacent clock regionusing BUFMRs

3、MMCMs clock outputs 0-3 driving theHPC in the same clock region

BUFR是regional时钟网络,顾名思义,它的驱动范围只能局限在一个clock region的逻辑,但是它可以同时驱动IO和内部逻辑。BUFR可以被如下节点所驱动:

1、所有能驱动BUFIO的节点

2、MMCMs clock outputs 0-3

3、General interconnect

BUFIO和BUFR的主要区别可以用下图概括:

BUFG是全局时钟网络,这个大家最熟悉了,它可以驱动所有的IO和逻辑,并且可以被Transceiver所驱动。

那既然有BUFG了还需要BUFR做什么呢?

BUFR相比BUFG的最大优势是skew和功耗都比较小,在源同步的设计中,这一点也是很关键的。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)