1

DeterminisTIc Latency

很多JESD204的系统包含多种多样的数据处理单元,并且他们处于不同的时钟域中,所以将导致无法确定的延迟。这些延迟将在链路层上电、断电、复位时产生随机的延迟。JESD204A没有提供处理接口延迟的方法,而在JESD204B中提供了两种机制(Subclass 1、Subclass 2)去解决延迟不定的问题。

数据链延迟定义为:并行的数据帧放到TX device 到并行的数据帧从RX device输出的时间差,这个时间差由frame clock 计算。延迟以frame clock为单位,并且越小越好,同时必须在系统上电、断电以及重新同步时,提供辅助的时间信息来满足输入的要求。

确定的数据链路延迟需要2个要求:

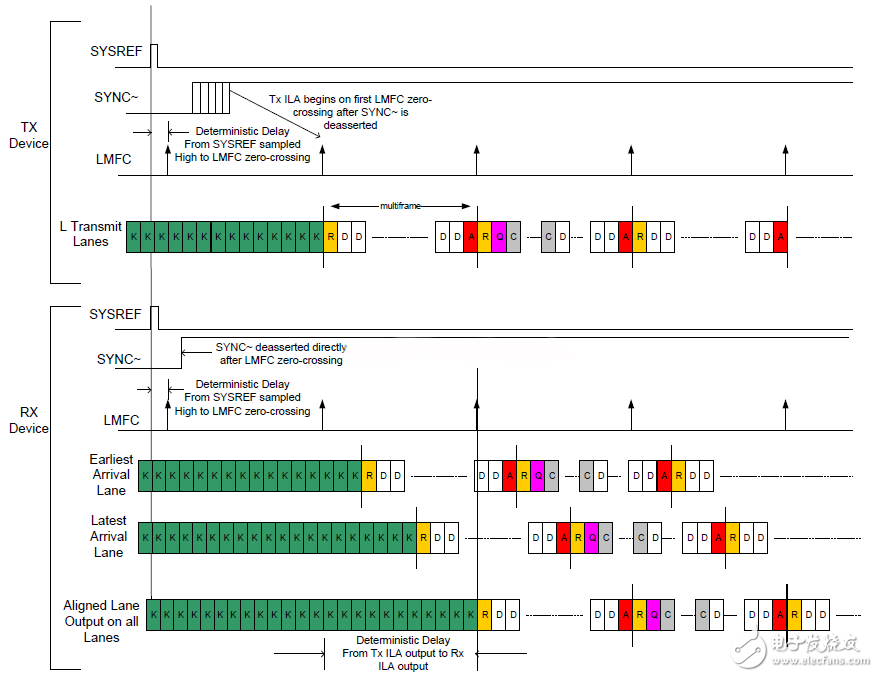

1. 在TX device,ILA(iniTIal lane alignment)必须保持所有的lanes同时启动,启动的时间为SYNC上升沿后的LMFC的第一个边沿或者是设定好的LMFC周期。

2. 在RXdevice,输入的数据必须缓存以消除TX SERDES lanes、物理通道、RX SREDES lanes带来的延迟。 数据在LMFC的边沿可以进行释放。

TX device的发送和和RX device 缓存的释放都会与LMFC对齐,因此固定的数据延迟决定于发送端与接收端LMCF的对齐程度。

为了更好的实现固定延迟的协议,需要注意以下两点:

1、 LFMC的周期必须大于数据链路的延迟。

2、 RX device的缓存区的缓存数据的时间必须大于数据链路的延迟。

3、 缓存区的大小在1到K之间。

以上3点是为了保证在RX缓存区释放数据时,所有的数据的发送数据都已经到达RX device。

最终的数据链的延迟将等于缓存区的大小*Tf。

1.1 EXAMPLE ImplementaTIon of determinisTIclatency in RX devices

要保证JESD204B数据链路的固定延迟,要求RXdevice在LFMC边沿到来之前可以缓存所有lanes上的ILA或者数据,但是释放缓存区的数据必须保证以下几个要求:

所有的lines上的数据必须有效,

如果RX buffers收到ILA序列,则认为数据的是有效的。

如果RX buffer没有收到ILA序列,RX buffer将在ILA序列发完后从新存储数据,并且buffer会在4个multiframe clock释放,因为一个ILA(启动序列)的长读为4。

数据链路层的的延迟可以表示为:Delay_link = △T_LMFC = TX_delay + Lane_delay + RX_delay.

1.2 No Support for Determisitic Latency(Device Subclass 0) (Informative)

Subclass 0 是为了向JESD204A兼容,所有没有固定延迟的功能。

1.3 Deterministic Latency Using SYSREF (DeviceSubclass 1)

在Subclass 1中,TX与RXdevice的通过用device clock抓取SYSREF信号的上升沿对齐LMFC,所以高精度的SYSREF和device clock将可以使系统延迟的最小化,建议用TX或者RX的device clock生成SYSREF信号(不是必须的)!

由于SYSREF信号的模式多样(periodic,one-shot(strobe-type,”gapped”periodic)),所以时钟生成器也许无法生成所有类型的SYSREF。同时为了适应系统,SYSREF可以关掉在正常的模式下,Subclss I必须满足以下要求:

RX Logic Devices必须有能力发出生成SYSREF信号的请求,时钟生成模块在接收到请求后,可以生成一个或者多个SYSREF脉冲给所有系统中的devices。如果使能,“generate SYSREF”请求信号可以在链路层发出重新同步的请求后的任何时间发出。

TX Logic Devices必须有能力发出生成SYSREF信号的请求,时钟生成模块在接收到请求后,可以生成一个或者多个SYSREF脉冲给所有系统中的devices。如果使能,“generate SYSREF”请求信号可以在链路层发出重新同步的请求后的任何时间发出。

TX和RXdevices必须有能力决定是否在下一个SYSREF的上升沿来临时进行frame&multiframe clock的对齐,具体的实现决定于device,但是要满足下列3个要求:

每一个被device捕获SYSREF脉冲都必须用于是否判断是否需要进行LMFC和frameclock的对齐。

Device可以通过来自引脚或者控制接口的命令决定在下一个SYSREF的脉冲是否要进行LMFC和Local frame clock的对齐。

Device可以通过来自引脚或者控制接口的命令去忽略以后所有的SYSREF脉冲信号。

NOTE:

对于Subclass 1devices,LMFC和Frame Clock的对齐于SYSREF只在device启动、链路传输失败、请求重新同步这3种情况下才是必须的,(也就是说在正常的数据传送情况下,LMFC和Frame Clock与SYSREF对齐一次就可以了)。

TX&RX devices必须给出device clock抓取SYSREF时,device clock的上升沿到LMFC上升沿的延迟。

1.4 EXAMPLE LMFC adjustment for deterministiclatency equal to multiframe period

延迟为一个multiframe的情况下,fifo的深度必须为K,同时要求fifo在multiframe clock的时钟边沿释放。

图32:TimingDiagram Illustration for deterministic latency equal to multiple of multiframeperiod

在图32中,TX和RXdevices有相同的抓取SYSREF信号的deviceclock上升沿与LMFC上升沿的延迟。保证了LMFC在TX和RX的一致。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)