本文以三星的SDR SDRAM(K4S64632)作为存储器,通过FPGA内部的M4K块作为移位寄存器不断的进行读进数据的方式,在不中断程序运行的情况下实现有效数据不间断的读进,设置3种采样模式,结果表明该设计提高了数据的分析范围和质量。

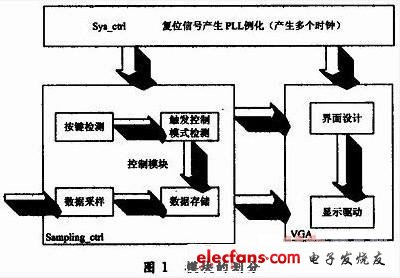

1 逻辑分析仪总体方案

逻辑分析仪包括:数据采样、数据存储、显示控制3大部分。由于Cyclone芯片EP1C3T144C8理想情况下最大频率可达到275 MHz,在实际设计中考虑到其误差,该设计的信号捕获精度定位在100 MHz。最多16路信号捕获输入通道,1路信号触发通道,可调的采样时钟/周期,3种信号采样模式,使用计算机的的显示器作为波形显示屏幕。

模块整体上是根据数据流的方向划分的,如图1所示。sys_ctrl模块对系统复位信号进行异步复位、同步释放,并且通过Cyclone芯片EP1C3T 144C8内部的PLL例化得到多个稳定可靠的时钟信号。Sampling_ctrl模块包含按键检测、触发控制、数据采样、数据存储等多个功能是采集控制的核心模块。VGA显示模块包含界面设计、字模数据寻址送显方式和显示驱动的时序控制。

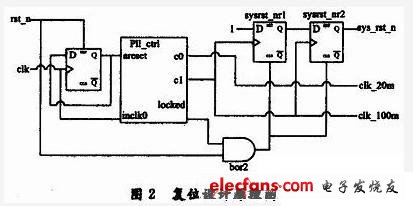

2 复位信号产生PPL例化

逻辑分析仪的复位设计如图2所示,这个模块设计里,先用FPGA的外部输入时钟clk将FPGA的输入复位信号rat_n异步复位、同步释放处理,然后将复位信号输入PLL,同时clk也输入PLL。在PLL输出时钟有效前,系统的其他部分都保持复位状态。PLL的输出locked信号在PLL有效输出之前一直是低电平,等PLL输出稳定有效之后拉高该信号。FPGA外部输入复位信号rst_n和locked信号相与作为整个系统的复位信号。从PPL输出端得到时钟不仅频率和相位上比较稳定,而且网络延时也相比内部的逻辑产生的分配时钟要小得多。

3 控制模块

通过FPGA内部的M4K块配置移位寄存器不断地读进新的采样值,数据采样回来后先经过SDRAM放入缓存FIFO中,然后把该FIFO中的数据上传到显示器。该模块的时钟是由PLL电路对FPGA输入的25 MHz晶振时钟倍频得到的。通过FPGA外部一组拨码开关控制输入电平为高或者低,从而设置不同的触发和采样模式。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)