Block Design 作为VIVADO的一大新神器,给用户设计带来了极大的方便,能够根据用户的定制需求自动选择、组合以及连接不同的IP。然而,其中不可控的Bug也给用户带来了一定的烦恼。这篇博文首先给出了一个Block Design的设计实例,带大家直观了解一下Block Desing。然后,列举了其中两个常见的Bug,给出其解决方法以及解决该类位的思路。

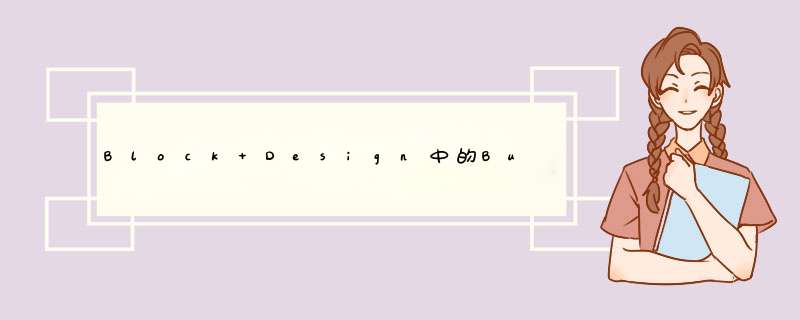

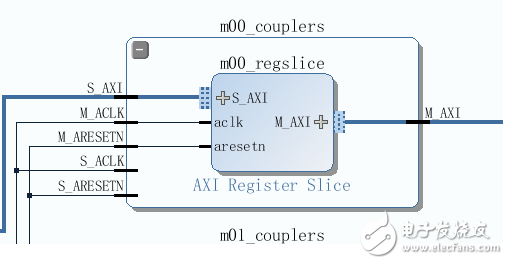

一、 Block Design示例如下图,设计一个基于AXI4-Lite的一个8*1的互连开关:

首先,我们只需要给出该设计模块的整体框架,是一个8*1的互连开关。然后,在引出对外的接口,并配置每个接口的参数。另外,还需要根据自己的需求设定互连开关中的一些参数,例如,需不需要slice来缓存、性能还是面积优先等等。最后,在参数配置完毕之后,就可以生成满足自己定制需求的交叉开关。如上图所示,自动添加了一下IP进去,如couplers、xbar等;在设计实现时,省去了设计者自己选择IP,手动添加互连的工作,带来很大的方便。

一、存在的Bug及解决方法 1. 多个功能类似的block design模块中的bug问题描述:

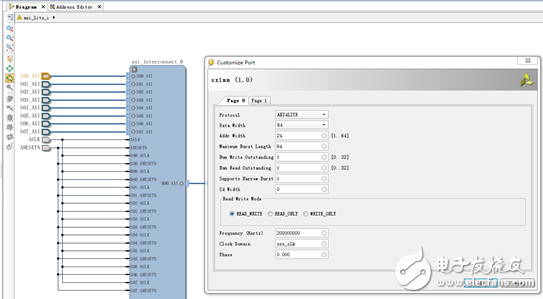

在设计中,往往需要多个Block Design(一下简称BD)模块,然而当多个BD的功能类似,导致两个BD中存在相同的IP时,两个BD在实例化IP模块时会使用相同的名字。例如,在一个系统中,用到了一个8*1的互连BD,用到了一个3*2的互连BD,两个BD都是互连开关,都有couplers模块,且发现实例化这些couplers模块时,使用相同的名字,如下图在0号master端口的couplers都使用m00_couplers_imp_PQAAIF的模块名。

此时,如果我们去跑系统的行为仿真,会发现总有一个BD的功能是不正确的,然而配置和逻辑是没有问题的。而且,在系统的综合实现时也会报错。

解决方法:

个人觉得这类问题是VIVADO中BD的硬伤,修改软件的参数或者BD模块的参数是改正不了的,直接修改源文件中的代码。当然,如果在VIVADO环境中去查看这些代码都是Read-Only模式的,是不能修改的。所以,我们要定位出问题的文件是哪个,然后在工程所在的文件夹中搜索,然后通过其它的编辑软件打开修改。例如,刚才的两个BD模块出问题的文件,分别位于E:\TD\TD.srcs\sources_1\bd\axi_lite_i\hdl和E:\TD\TD.srcs\sources_1\bd\axi_interconnect\hdl,我们只需修改其中任意一个,将名字相同的模块名改为不同即可。

1. 无法自动添加功能需求的IPBD功能的强大之处就在于其能够根据用户的需求(设定一些参数)自动添加相应的IP,然而,有时候却无法添加,给用户带来意想不到的错误。

问题描述:

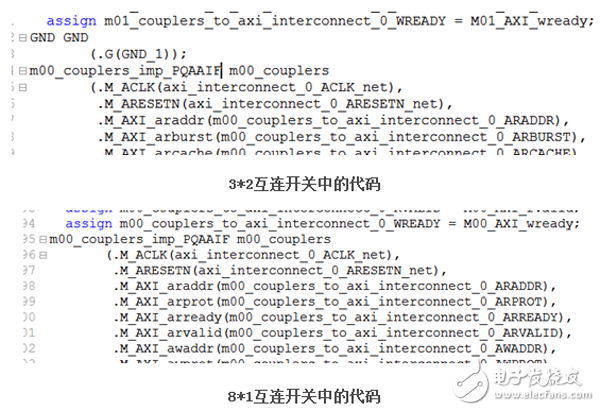

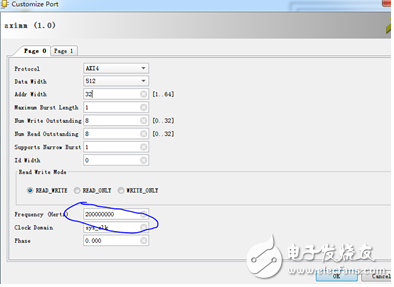

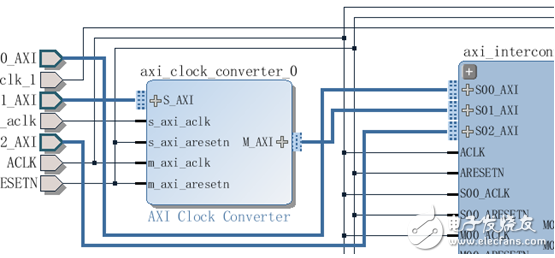

仍以上述的3*2互连开关为例,该互连开关能够连接不同时钟频率的模块,自动完成不同时钟域的转换。我们仅需要在配置端口处配置该端口所连模块的工作频率,例如在slave端口处,如果设定与互连开关不同的频率,该端口处Couplers就会自动添加时钟转换模块的IP。

然而,在master端口处采用类似的方法,我们在生成BD之后,却发现没有相应的时钟转换模块。相同的 *** 作,在不同类型端口处去有不同的生成结果。

解决办法:

这类的Bug肯定会导致逻辑的错误,因为少了一些IP。所以,建议各位设计者在使用BD时,要抱着怀疑的态度,在BD生成完毕之后,在点击去查看一下,看所需要的IP是否添加完整,不要给后续的调试带来极大的麻烦。

针对上述的问题,我们可以采用两种方法:

1. 当发现所要的IP没有添加进去时,我们可以分析该IP所在的位置,自己手动添加该IP,然后互连到相应的位置。如下图所示,少了时钟转换模块,我们将其手动添加到外部,也能完成相应的逻辑功能。

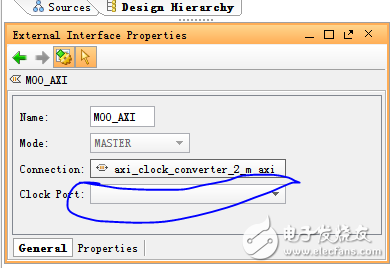

2. 寻找没有自动添加的原因。这个解决方法有点可遇而不可求,有的时候就是软件中的一点小Bug,你稍微修改一下模块的参数即可。比如刚才的问题,我们可以在该端口的属性窗口中将clock port的选项给选择正确了即可(这个 *** 作按道理是软件自动完成的,因为另一端的端口处不用自己选择也能自动添加正确)。

以上笔者列举了BD设计中常见的Bug,由于篇幅原因无法将其他的一一列举出来。如果您在设计中发现其它的Bug,暂时又难以解决,可以联系我QQ:657428214,我们一起探讨解决。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)