SemiWiki的Eric Esteve刚刚发表一篇博客,标题为 “再见,DDRn协议”。博客中Esteve承认这份博客将引起轰动,且声称 “ 今后数年主流机器极有可能都将使用DDR4。 ”英特尔于3月19日发布的近期公告也宣布 “今后开发的处理器都将支持DDR4 SDRAM”。相较于仅仅“宣布支持”未来产品, Xilinx 已经在展示其全新Kintex UltraScale All Programmable器件的上的DDR4支持。(请参阅 “Ready for DDR4-2400? Need the bandwidth? Need the lower power consumpTIon? Watch this 8-minute video...”)

Esteve进一步证实了DDR4 SDRAM今后数年将占据牢固地位。他写道:“我们可以想见今后两年DDR4将应用于企业级市场,随后将应用于桌面电脑领域,DDR4内存价格将相当于或低于DDR3内存价格水平。 ”如果预见成真,DDR4 SDRAM将进入嵌入式系统,原因是届时DDR4 SDRAM不仅可提供最高性能,而且每比特的成本也将是最低的。

然而,Esteve指出 “DDRn系列中的'4'肯定是最新款……”,[(原文如此) ,我觉得Esteve所指的是在博客中所指的一款。 ]

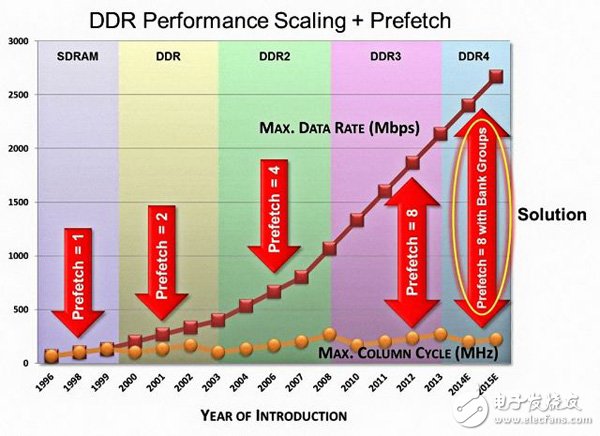

Esteve发布了过去二十年来DDR标准的演进以及最大数据速率:

哪些产品将会取代DDR?Esteve也对此有所提出:“最有希望的是基于高速串行 SerDes的产品,采取时钟恢复可简化SoC和板级实现。 ”这类内存样品已经出现,被称作混合内存立方体(Hybrid Memory Cube ,HMC),该项目由Hybrid Memory Cube ConsorTIum赞助实施。Xilinx、Micron和Open Silicon是该组织的创办发起人。

HMC在DRAM和主机处理器或SoC之间加入高速逻辑层。逻辑层管理DRAM,使得内存通过四个高速串行链路在系统中运行,每个高速串行链路需要16个高速串行收发器( 完全连接后共有64收发器)。Xilinx Virtex-7 FPGA 上的SerDes端口完全支持HMC 10Gbps和12.5Gbps收发器速率。每个设备设置多达96个 GTH收发器,便于Xilinx 7 系列FPGA轻松使用HMC设备的高带宽。Xilinx UltraScale FPGA中的GTH收发器技术利用64个收发器将HMC接口带宽扩展至15Gbps。Micron的首个160 GB/s内存带宽的商业2Gbyte HMC现已发样。

(注: HMC于今年2月向其应用成员,包括Xilinx,发布了第二代(Gen2)规格的初稿,支持双倍速率。在发布会上,Xilinx产品组合与解决方案销售副总裁Hugh Durdan指出,“目前正出货的UltraScale器件在设计上支持该规格,针对高带宽应用可以降低风险,并加速上市进程。”

同样, MoSys Bandwidth Engine 2属于一种器件,即在使用多个高速串行通道的系统添加快速访问内存来实现总传输速率达到250Gbps(请参见 “MoSys Bandwidth Engine 2 adds “Go Juice” to Kintex UltraScale FPGA via mulTIple 15.625Gbps lanes at ....”)

并未出现任何迹象表明全新DDR4内存接口处在随时消失的危机中。Eric Esteve指出,DDR4 SDRAM仍将盛行数年,短期和中期内仍将扩大其应用范围。

另外需要告诉大家的是,Xilinx拥有 Memory Interface Generator (MIG) 工具 ,可以自动地为多个通用内存接口以及那些混合接口设计(比如您不得不在一个器件上控制多种内存)生成控制器与PHY。以下为解释MIG工具的短视频:

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)