伴随着现代大规模集成电路制造工艺的快速发展,设计工程师必需直面芯片制造过程中可能产生的物理缺陷。现今流行的可测试性设计(DFT:Design For Testability)应运而生,并为保证芯片的良品率担任着越来越重要的角色。设计中,存在对测试覆盖率有较大损害的两种情况:一种存在于数字逻辑-模拟逻辑(包括存储器)输入-输出处之阴影部分,另一种存在于特定的多芯片封装情况下未绑出的输入-输出焊垫处。二者的共同点在于:测试模式下部分逻辑的不可控或不可观测。

设计背景

本文探讨的设计目标是一个来自意法半导体的数字音频信号处理芯片,要求对数字功能逻辑进行扫描链测试,覆盖率达到98%以上。其功能逻辑中存在一些模拟模块,如锁相环、模数转换器和一些存储器单元等。更为重要的是,该芯片需要基于不同的应用系统需要,不但需要单独封装形式,也需要多芯片共享同一封装。这样,在某些多芯片封装中,就有部分焊垫未引出或接地。而测试的设计初衷是产生一组测试向量适用于所有封装形,就要求考虑最严格的封装下可用的管脚资源。

DFT设计有两个基本原则:可控制性和可观测性,即DFT设计要求所有输入逻辑是可控的和输出逻辑是可测的。显然,考虑到本设计中的模拟模块接口和封装形式的资源有限性,不可控逻辑和不可观测逻辑对不小于98%的目标测试覆盖率给出了很大的挑战。

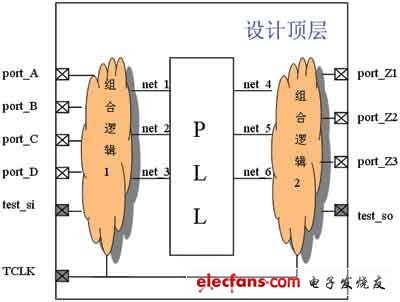

如图1所示,在某种芯片封装情况下,除信号test_si和test_so外,其余焊垫并未绑出(接地或悬空),从而造成信号port_A、port_B、port_C和port_D的不可控,以及信号port_Z1、port_Z2和port_Z3的不可观测(悬空)。导致很多相关逻辑不能正常参于DFT测试,测试覆盖率受到较大的损害。

图1 封装造成的测试逻辑不可控和不可测

DFT设计的可控制性和可观测性是通过原始的管脚来实现的,事实上功能设计不可能专门为DFT保留足够多的管脚。如图2所示的数字-模拟接口,由于PLL模块的存在,显然信号net_1、net_2和net_3上得到的测试结果不可直接观测(不可测),组合逻辑1相应的测试覆盖率降低了;同时,由于PLL模块的存在,信号net_4、net_5和的net_6不能直接赋值(不可控),导致组合逻辑2的部分逻辑不能正常参于DFT测试,相应的测试覆盖率受到较大的损害。总的来说,芯片的测试覆盖率降低了。

解决方案

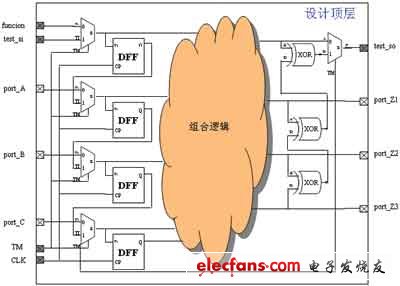

针对设计中的上述情况,可以通过适当添加测试点的方式,使原来不可控和不可测的逻辑变化反映到扫描链上,使之变得间接可控和可测,以期提高整个芯片的测试覆盖率和测试效率。

对于图1所示的某些封装中,不可控和不可测的未绑出(接地或悬空)管脚,图3给出了相应的定制的解决方案。

图3 添加控制点和观测点提高测试覆盖率(封装部分管脚未绑出情况)

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)