设计功能的调试是一件持续的事情:从架构设计开始,贯穿逻辑和物理实现整个过程,并且在出带后也不会停止。一旦原型硅片被制造出来并被安装在目标板上,系统验证工程师就要执行一连串的系统级测试,并处理任何检测到的故障。

理解造成这些故障原因的关键在于内部信号值的可视性。许多工程师会在设计阶段忽视这种后硅片要求,但最新数据表明,从原型硅制造出来到大批量生产的时间越来越长,因此急需改进系统级硅片调试。

设计验证的改善不能彻底缩短系统级调试时间。由于验证工具受容量和性能的限制,工程师在完成出带前的验证时必须经常权衡精度和完全性与可用时间和资源之间的关系。另外,软件在硅片制造出来之前不可能做到没有任何缺陷。而且在制造过程中还会引入物理缺陷。

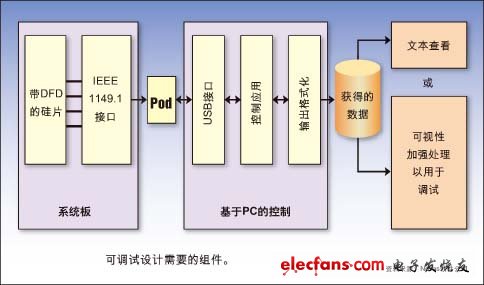

可调试设计(DFD)方法可以帮助人们在系统级验证阶段就深入了解内部硅片行为。大多数DFD实现的一个重要方面是复用现有的可测试设计(DFT)逻辑,如扫描链和边界扫描控制器(IEEE1149.1)。这些结构可以方便地通过与PC相连的调试端口提供对硅片信号数据的访问。

分析工具可用来处理采集到的数据,并作进一步的图形化显示。DFD系统在系统验证工程师和设计师之间架起了联系的桥梁。它提供了对硅片信号数据的优秀可视性,提高了调试产能,缩短了系统验证时间。以下针对DFD给出了一些建议。

要

1.考虑调试必须实时完成还是可以采用时间插入技术。实时调试可以详细查看高带宽的信号信息,适用于具有大量嵌入式软件交互的系统。时间插入方法则更容易实现,可以提供更多的数据,但带宽较低。

2.复用DFT。大多数设计包含扫描链和JTAG控制器,这些设施可作为DFD的基础。在器件工作时进入调试模式并通过JTAG移出捕获的数据要求额外的复位和时钟控制逻辑。TAP控制器必须用在线调试 *** 作指令进行扩展,这些指令可以从PC上的控制程序中装载。

3.尽可能使用非破坏性扫描来实现“一停二看三通过”的调试方法。寄存器值会在扫描移位中遭到破坏,除非硬件能阻止这种破坏,或DFD控制软件能透明地重新装载正确的值。

4.计划好整个DFD。在片上放置DFD逻辑只是其中的一个步骤。电路板必须包含芯片调试口和插座连接器之间的连线。要确保电路板连接器和PC之间的电缆兼容性。控制程序是在用于JTAG测试的软件库基础上开发的,必须格式化捕获的数据以便调试工具的进一步分析。

图:可调试设计需要的组件

不要

1.在硅片制造出来后才决定调试策略,这对提高内部信号的可视性来说已经太晚了。在编码开发前就要在器件规范中整合DFD概念。

2.认为软件开发环境可以提供足够的硬件调试能力。内部信号数据有时可以被SDE访问,但通常仅限于结构化寄存器,如数据和地址寄存器。高效的硬件调试要求实现状态机寄存器和其它关键信号的可视化。

3.忽略时钟处理和数据交互。要确保控制逻辑不会无意间在时钟线上注入毛刺。另外,要监视跨时钟域的数据,并确定系统停止后是否有效。

4.忽视在出带前验证DFD逻辑。DFD是器件的功能特性,必须加以规范和验证。

5.忘记考虑在采集到信号数据后做什么。检查文本化值对数据和地址寄存器来说已经足够,但其它寄存器数据最好采用面向HDL的调试系统提供的波形、源、原理图和事务窗口进行分析。需要包含将信号值输出为数值信息转储或快速信号数据库等格式的能力,以确保这种连接的存在。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)