现如今,赛灵思 FPGA 上采用低电压差分信令 (LVDS) 输入,仅需一个电阻器和一个电容器就能实现模拟输入信号的数字化。由于数百组 LVDS 输入驻留在生成电流的赛灵思器件上,因此理论上可通过单个 FPGA 芯片实现数百模拟信号地数字化。

我们的团队近期在为数字化 128 元件线性超声波阵列换能器信号研究选项时,发现了一个极具潜力的设计领域——可用 3.75MHz 中央频率配合 5 位分辨率对限带输入信号进行数字化。下面我们来看看该演示项目的详细情况。

2009 年,赛灵思推出了一款 LogiCORE 软 IP 核,其外加一个外部比较器、一个电阻器和一个电容器即可实现能对频率高达 1.205 kHz 的输入进行数字化的模数转换器 (ADC)。若让 FPGA 的 LVDS 输入(而不是外部比较器)结合增量调制器 ADC 架构,仅需一个电阻器和一个电容器,就能对频率高得多的模拟输入信号进行数字化。

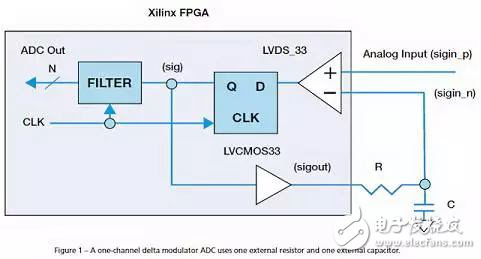

1、ADC 拓扑与试验平台图 1 是采用 LVDS 输入且在赛灵思 FPGA 上实现的单通道增量调制器 ADC 的框图。在这里,模拟输入驱动非反相 LVDS_33 缓冲器输入,而输入信号范围则基本为 0 至 3.3 伏特。LDVS_33 缓冲器的输出在远远高于输入模拟信号频率的时钟频率下采样,并通过 LVCMOS33 输出缓冲器和外部一阶 RC 滤波器反馈给反相 LVDS_33 缓冲器输入。就适当选择的时钟频率 (F)、电阻 (R) 和电容 (C) 而言,只需采用该电路,反馈信号就可跟踪输入模拟信号。

例如,图 2 在 F = 240MHz、R = 2K、C = 47 pF 时分别以黄色和蓝色显示了输入信号(通道 1)和反馈信号(通道 2)。所显示的输入信号由 Agilent 33250A 函数信号生成器采用其 200MHz 12 位任意输出函数信号功能生成。我们用 Tektronix DPO 3054 示波器计算得出的输入信号的傅立叶转换则显示为红色(通道 M)。在这些频率下,示波器探针的输入电容(以及接地问题)确实会弱化示波器中显示的反馈信号,但图 2 同时也展示了该电路的工作情况。

我们通过对 1Vpp3.75MHz 正弦波应用 Blackman-Nuttall 窗,定义了图 2 所示的带限输入信号。虽然与理论视窗信号相关的噪声底限几乎比与中央频率相关的量级低 100 dB,但 Agilent 33250A 函数信号生成器的 200MHz 采样频率及 12 位分辨率会导致远远低于理想水平的演示信号。许多中央频率接近 3.75MHz 的超声波换能器产生的输出信号自然会受到频带限制,这是因为换能器机械属性的缘故,因此该输出信号是使用这种方法的理想信号源。

我们使用 DigilentCmod S6 开发模块得到了图 2 所示的图形,该开发模块在支持 8 个 R/C 网络和各种输入接插件的小型定制化印刷电路板上安装了赛灵思 Spartan-6XC6SLX4 FPGA,允许原型系统同时对多达 8 个信号进行数字化。

每个通道都以 50 欧姆接地电阻并行端接,从而可使同轴线缆与信号生成器正确端接。必须注意的是,为了实现这一性能,我们将 LVCMOS33 缓冲器的驱动电流值设置为 24 mA,将压摆率设置为 FAST,如图 5 示例 VHDL 源代码中所述。

此外,该定制化原型电路板还支持使用 FTDIFT2232H USB 2.0 迷你模块,我们用其将封包的串行比特流传输给主机 PC 进行分析。图 3 是输入图 2 模拟信号后原型电路板所生成的比特流的傅立叶转换强度。与 240MHz 采样频率的次谐波相关的峰值清晰可见,与输入信号相关的峰值频率为 3.75MHz。

2、大量的抽头

为比特流应用带通有限脉冲响应 (FIR) 滤波器,可生成模拟输入信号(ADC 输出)的 N 位二进制表示法。但由于数字比特流的频率远远高于模拟输入信号,因此您需要使用有大量抽头的 FIR 滤波器。但是,被过滤的数据只有 0 和 1 两个值,因此无需乘法器,只需加法器将 FIR 滤波器系数相加。

图 4 所示的 ADC 输出在主机 PC 上采用有 801 个抽头的带通滤波器生成,其中央频率为 3.75MHz,是我们使用免费在线 TFilter FIR 滤波器设计工具设计而成的。该滤波器除了 2.5MHz 至 5MHz 带通之外,还有 36dB 或更大衰减,在 3 和 4.5MHz 之间有 0.58dB 的波纹。

图 4 所示的 ADC 输出信号分辨率约为 5 位,这基本上由过采样速率决定,您可使用针对较低输入频率优化的设计实现更高的分辨率。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)