在嵌入式系统中,很容易在系统核心找到 FPGA。这是因为 FPGA 能同时并行执行多个功能,并具有确定性的响应。很多嵌入式系统还包含一个处理器,用来处理通信任务、内务管理、调度任务以及通常在软件中执行的其他任务。

这种 FPGA 与处理器的组合会增加系统的 SWAP-C。SWAP-C 是指解决方案的尺寸、重量、功耗和成本。显然,同时使用处理器和 FPGA 不仅会增加材料成本,同时还会增加偶生工程成本(NRE)。此外,设计与验证工作变得更加复杂。两个器件还需要更多板级空间,这会增大解决方案的尺寸和重量。电源结构也比只用一个器件时复杂,这进一步影响 SWAP-C。

尽管难以用软件驱动的处理器来实现通常由 FPGA 执行的功能,但在 FPGA 内部实现处理器,通常能让设计大受裨益。

对于在赛灵思 FPGA 中实现处理器,我们有多个选择:

PicoBlaze– 8 位高确定性微控制器(见赛灵思中国通讯 54 期,“充分发挥 PicoBlaze 微控制器的优势。”)

MicroBlaze– 32 位 RISC(精简指令集计算机)处理器,可针对众多应用在性能和面积方面进行定制。

Zynq UltraScale MPSoC 和 Zynq-7000 SoC将硬化的嵌入式 ARM 处理器和可编程逻辑完美集成在单个芯片上。(如需了解有关 Zynq-7000 SoC 使用方面的信息,敬请查阅MicroZed Chronicles)

本文中,我们将深入了解如何在 FPGA 设计中实现赛灵思 MicroBlaze 处理器以减小 SWAP-C。

什么是 MicroBlaze

MicroBlaze 是 32 位软核处理器。这意味着它是一款可先定制,然后综合,最后布局布线到目标 FPGA 的逻辑资源中的软 IP 核。每个 MicroBlaze 处理器实例都是自定义的,包含 FPU(浮点单元)、MMU(存储器管理单元)以及指令与数据缓存这样的高级特性。

用户可在 MicroBlaze 处理器上运行一系列 *** 作系统,包括 FreeRTOS、Micrium uc/OSiii 和 Linux。用户还可以运行裸机代码。实例的软特性可确保不存在过时问题。简而言之,MicroBlaze 处理器是一款功能非常强大的嵌入式系统开发工具。

创建 MicroBlaze 系统

在设计中实现 MicroBlaze 处理器是赛灵思 Vivado HL WebPACK 版本的一项标准功能。

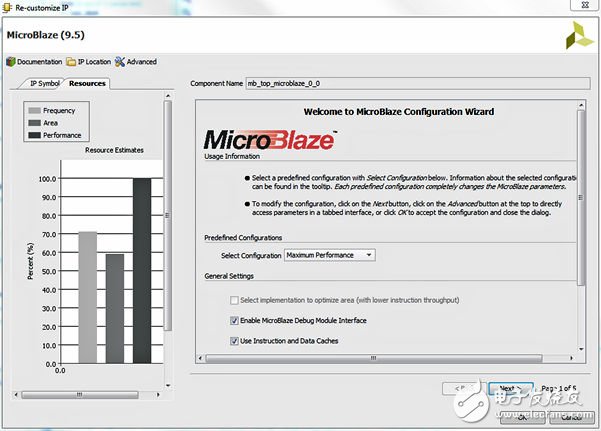

首先要做的是在 Vivado 中创建新项目,并添加一个新的方框图。然后,我们可以从 IP Catalog 中选择添加 MicroBlaze 处理器核。一旦我们将 MicroBlaze 处理器放在方框图中,应针对所需的性能对其进行自定义。打开要自定义的 MicroBlaze 处理器后,会出现五个处理器自定义页面中的第一个。在第一页中,我们可以为处理器核选择所需的性能,如图 1 所示。本例中,我们将开发一个高性能 MicroBlaze 处理器。

图 1:选择 MicroBlaze 的配置。

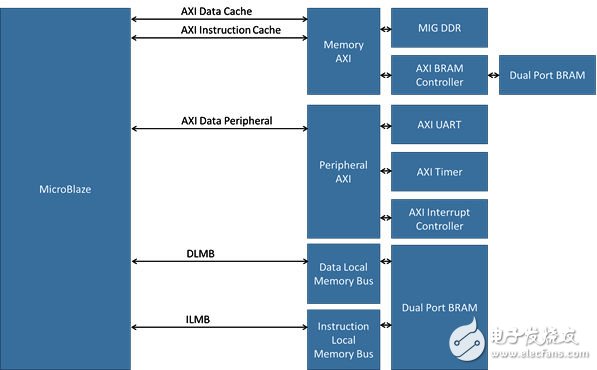

要创建一个基础的系统,我们需要以下 IP 核:

MIG(存储器接口生成器)– 提供 DDR 存储器接口

AXI UART lite – 双击它可设置 RS232 选项。默认设置是 9600bps,无奇偶校验位,一个停止位。

AXI 定时器

AXI 中断控制器 – 需要一个连接模块驱动来自定时器和 AXI UART lite 的中断。

用于 AXI 数据和指令缓存的 AXI BRAM 控制器和 BRAM

用于输出 166.667MHz 时钟和 333MHz 时钟的时钟向导

MicroBlaze 调试模块

用于连接定时器和 UART 的 AXI 外设互连

用于连接 MIG (DDR) 和 AXI BRAM 控制器的 AXI 存储器互连

针对 MicroBlaze 时钟域的处理器复位系统

针对存储器接口生成器时钟域的处理器复位系统

这些模块的连接架构如以下的图 2 所示:

图 2:高级方框图

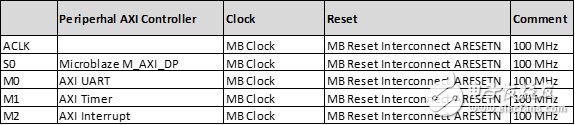

我们将 100MHz 时钟作为时钟向导的输入,该向导利用 MMCM(混合模式时钟管理器)生成 100MHz、166.667MHz 和 200MHz 的时钟。MicroBlaze 处理器将采用 MMCM 的 100MHz 输出来运行,而其他时钟将被用于存储器接口生成器。下面的表 1 和表 2 给出了 AXI 互连的配置:

表 1:外设 AXI 互连,时钟和复位配置

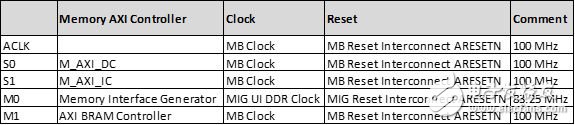

表 2:存储器 AXI 互连,时钟和复位配置

配置 DDR 存储器

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)