无线系统的概念与设计实现之间存在巨大的差异。要缩小这种差异通常都要涉及到几组来自各领域的工程师团队(比如RF、SW、DSP、HDL和嵌入式Linux®),并且很多情况下项目在开发的早期阶段便由于难以协调各设计团队而偏离了原先计划。

本系列文章分为四个部分,将讨论平台和工具的进步;这些技术进步允许开发人员快速进行无线系统的仿真与原型制作,同时建立与保持投入生产的可实现路径。作为实际过程的一个示例,我们将对无线SDR平台进行原型制作,该平台可接收并解码自动相关监视广播 (ADS-B) 信号,以便我们检测并汇报附近飞行中的商用飞机的位置、高度和速度。本例中需用到MATLAB®和Simulink,以及集成和内嵌硬件/软件的技能。硬件平台将采用ADI/Xilinx®软件定义无线电 (SDR) 原型制作系统。使用MATLAB和Simulink®后,将执行下列任务:

设计用来解码ADS-B消息的信号处理算法

仿真接收ADS-B信号的RF接收器

生成C语言代码和HDL代码

以目标收发器和FPGA上的记录数据和实时数据验证HDL代码

最终得到一个能够在适于生产的硬件上实现的可行RF SDR设计,我们将把它带到当地机场来验证性能和功能。

该文章系列有四部分,第一部分将讨论ADI/Xilinx SDR原型制作系统、该系统的功能和优势,并简要描述工具流程。第二部分将回顾自动相关监视广播 (ADS-B) 信号,并解释仿真时如何在MATLAB和Simulink中解码它们的信息。第三部分将讨论和演示如何使用环路中硬件 (HIL) 并以目标收发器捕捉信号,并同时在Simulink的主机中进行信号处理以便验证。第四部分将说明如何通过第二部分开发并在第三部分验证的算法,并使用MathWorks的HDL编码器以及嵌入式编码器生成代码,然后在生产硬件中进行部署;最后,我们将在机场采用真正的ADS-B信号来 *** 作平台。

简介随着人们对通信方式和手段的需求呈指数式增长,方便而经济高效地修改无线电设备也随之成为一项重要的业务。在这样的背景下,软件定义无线电技术最近得到了广泛的部署,因为这项技术推动通信向着灵活、高性价比、功能更强大的方向发展1。SDR系统的目的是在软件和可重复编程逻辑中部署尽可能多的调制/解调和数据处理算法,以便通信系统能够仅通过更新软件和可重复编程逻辑而轻松进行再配置,并且无需更改硬件平台。

随着片上系统 (SoC) 的出现(比如集CPU的灵活性与FPGA的处理能力于一体的Xilinx Zynq.® All Programmable SoC),设计人员终于能够将SDR系统的数据处理功能和其它处理任务纳入单个器件中。数据调制/解调算法等处理密集型任务分流至器件的可编程逻辑,而数据解码和渲染、系统监控和诊断以及用户界面等任务延缓至处理单元进行。

同时,无线系统的原型制作数十年来一直是个争论不休的话题,而最近几年才刚出现针对FPGA的完整设计流程 — 从模型创建到完整实施 — 这要归功于像MathWorks的MATLAB和Simulink等建模和仿真工具的革命。无线系统的原型制作正在改变工程师和科学家工作的方式,它将设计任务从实验室和现场带到了桌面上2。现在,工程师可以对整个无线系统(比如SDR系统)进行建模,从而可观察系统的表现,并在现场实际实施之前进行调节。这样做有很多好处,比如加快系统集成、减少对设备的依赖。此外,完成SDR系统的Simulink模型之后,C语言代码和HDL代码可自动生成,然后部署到Zynq SoC上,从而节省时间并避免手动编码错误。将系统模型链接到快速原型制作环境可进一步降低风险,因为后者允许SDR系统在实际条件下运作。

该文章系列有四部分,第一部分将讨论ADI/Xilinx SDR快速原型制作系统、该系统的功能和优势,并简要描述工具流程。文章解释了ADI RF IC技术和参考设计硬件与软件如何降低设计技巧,从而使客户减轻风险,并缩短产品上市时间。

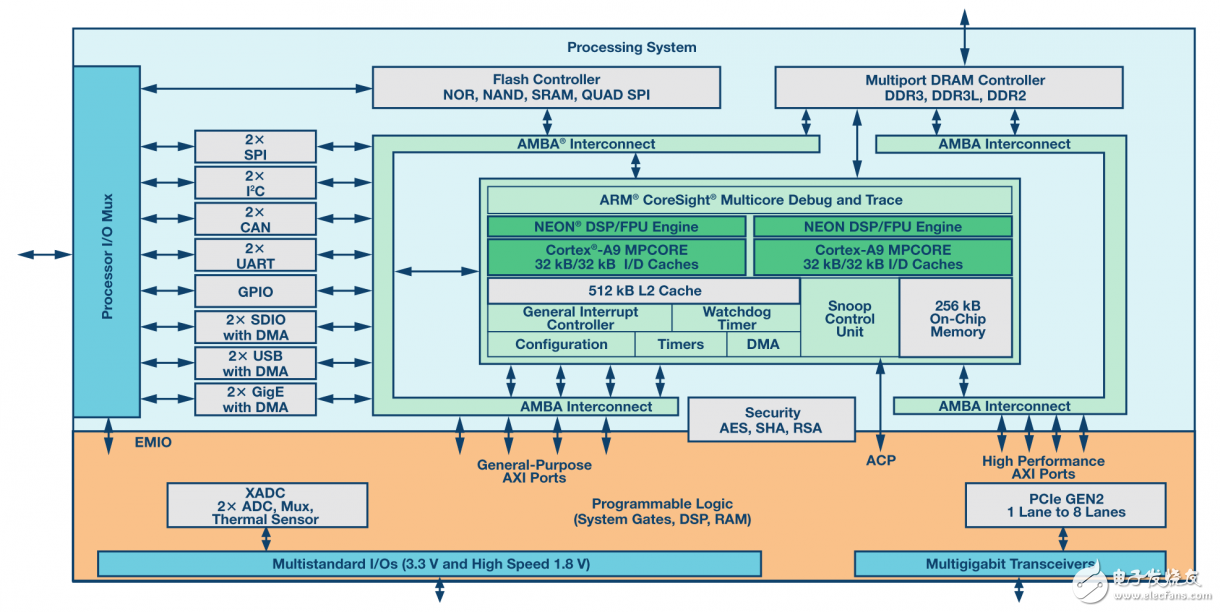

用于SDR的Zynq当需要执行数据处理、通信和用户界面等具有不同处理带宽要求和实时限制的任务组合时,需要用到高级SDR系统。为了实现这样的系统,所选的硬件平台必须鲁棒且可扩展,同时还需为将来的系统改进和扩张创造条件。Xilinx Zynq-7000 All Programmable SoC满足这些要求,提供高性能处理系统以及可编程逻辑,如图1所示3。可编程逻辑配上处理系统便具有了出色的并行处理能力、实时性能、快速计算能力以及连接的多样性。

图1. Xilinx Zynq SoC功能框图

Zynq SoC的处理系统包括一个双核ARM® Cortex®-A9处理器和一个NEON协处理器,以及多个用于加速软件执行的浮点扩展单元。为了完全发挥系统的能力,可以在双核ARM处理器上采用嵌入式Linux或实时 *** 作系统。该处理器是自足的,可在不配置可编程逻辑的情况下使用,这点对于软件开发人员来说很重要,他们可以与设计FPGA结构的硬件开发人员同时进行代码的开发工作。

在可编程逻辑方面,该器件拥有多达444,000个逻辑单元和2,200个DSP Slice,可提供巨大的处理带宽,允许Zynq设备应对各种充满挑战的信号处理应用。5个高吞吐速率的AMBA®-4 AXI高速互连将可编程逻辑紧密地耦合到处理系统,提供相当于3,000以上引脚的有效带宽4。

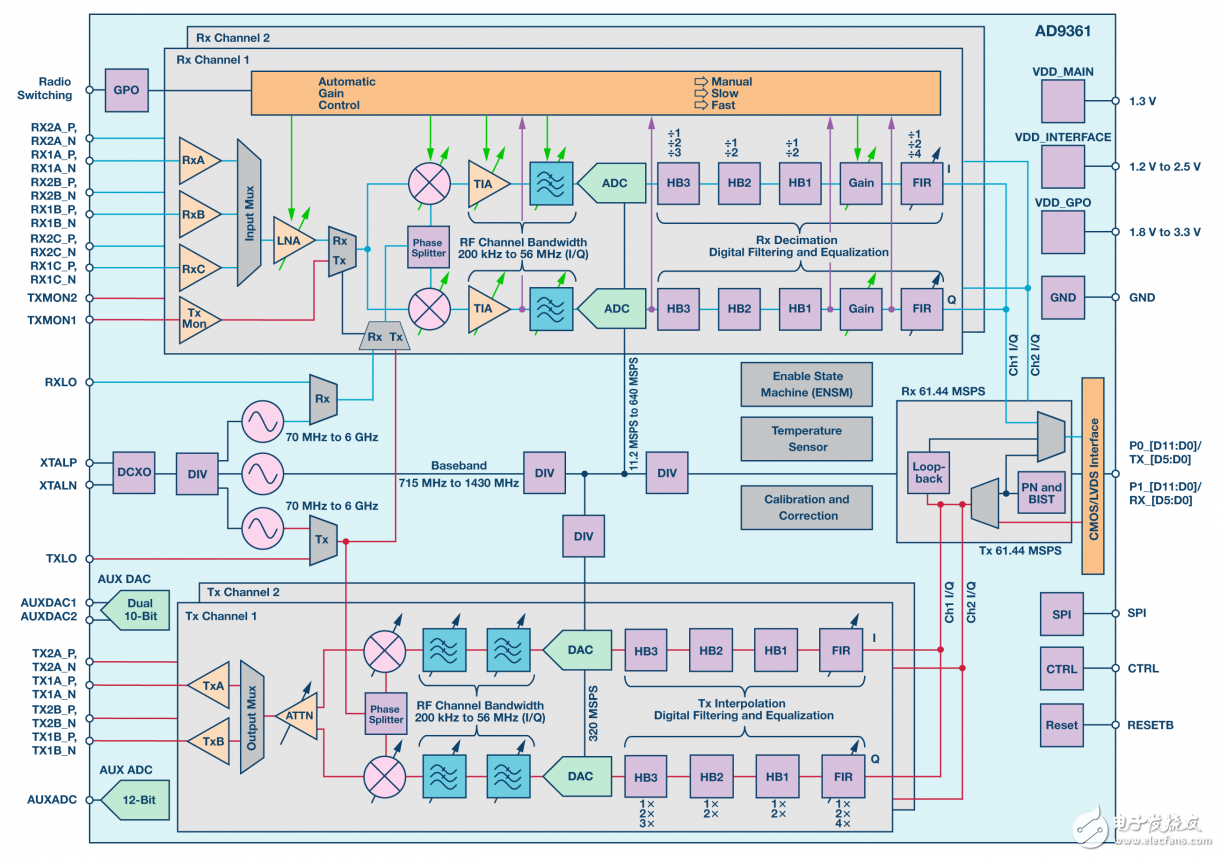

用于SDR的AD9361捷变宽带RF收发器近年来,ADI公司将革命性的SDR产品推向了市场,以支持不断变化的SDR要求和系统架构。在这方面,ADI最重要的产品包括AD9361/AD9364集成式RF捷变收发器。AD9361 (2 × 2)5和AD9364 (1 × 1)6是用于SDR架构的高性能、高度集成的RF收发器IC,适合无线通信基础设施、防务电子系统、RF测试设备和仪器,以及通用软件定义无线电平台等应用。这些器件集RF前端与灵活的混合信号基带部分为一体,集成频率合成器,为处理器或FPGA提供可配置数字接口,从而简化设计导入。这些芯片工作频率范围为70 MHz至6 GHz,涵盖大部分特许执照和免执照频段,通过对AD9361和AD9364器件编程可改变采样速率、数字滤波器和抽取参数,使该芯片支持的通道带宽范围为低于200 kHz至56 MHz7。图2显示了AD9361器件的功能框图。

图2. AD9361功能框图

为了帮助客户缩短产品上市时间并减轻整体开发负担,ADI公司更进一步,提供的SDR解决方案可用于具有无缝FPGA连接能力的完整生态系统中,为完整的无线电系统设计提供快速原型制作和开发环境。AD-FMCOMMSx-EBZ快速开发和原型制作板属于高速模拟FMC模块,集成AD9361或AD9364捷变RF收发器IC或分立式信号链,可无缝连接Xilinx FPGA开发平台生态系统。这些板可完全通过软件定制,无需更改任何硬件,提供可供下载的Linux驱动程序和裸机软件驱动程序、原理图、电路板布局文件和有助于设计的参考材料,可前往ADI的Wiki知识库获取。表1总结了不同FMCOMMSx平台的产品特性。

表1. FMCOMMSx平台

平台 : AD-FMCOMMS5-EBZ

产品特性: 该SDR快速原型制作板集成两个AD9361 2 × 2捷变收发器IC,能够为4个接收器通道和4个发送器通道提供完全同步能力,可创建4 × 4 MIMO系统的任意子系统。支持宽带70 MHz至6 GHz和2.4 GHz调谐端口。AD-FMCOMMS5-EBZ资源页面(wiki知识库):

平台 :AD-FMCOMMS4-EBZ

产品特性:该1 × 1 SDR快速原型制作板集成AD9364捷变RF收发器IC,可经软件配置在2400 MHz至2500 MHz范围内实现最高RF性能,或者可经软件配置工作在AD9364的70 MHz至6 GHz完整RF调谐范围内,以进行系统原型制作和开发。AD-FMCOMMS4-EBZ资源页面(wiki知识库): fmcomms4-ebz

平台 :AD-FMCOMMS3-EBZ

产品特性:该2 × 2型号的SDR快速原型制作板集成AD9361捷变RF收发器IC,支持AD9361的70 MHz至6 GHz全RF调谐范围。该套件非常适合寻求具有宽调谐能力的统一开发平台的无线通信系统架构师。AD-FMCOMMS3-EBZ资源页面(wiki知识库):

平台 :AD-FMCOMMS2-EBZ

产品特性:该2 × 2 SDR快速原型制作板集成AD9361捷变RF收发器IC,经调谐可在2400 MHz至2500 MHz范围内实现最高RF性能。该套件适合寻求最优系统性能,并要求在RF频谱定义范围内满足AD9361数据手册中规格的工程师使用。AD-FMCOMMS2-EBZ资源页面(wiki知识库):

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)