摘要: 介绍了一个基于FPGA 的多通道信号采集电路。该电路以FPGA 芯片XC3S400 作为电路的主控制器,采用电子开关ADG708 对7 路信号进行了循环采集,使用AD7667 作为模数转换器,由主控制器FPGA 控制,将采集到的模拟信号转换为数字信号。然后,通过单片机CY7C68013 与上位机通信,将采集到的信号通过上位机软件读出并画图显示。通过试验已验证了该采集电路的功能的有效性。

0 引言数据采集是信号处理过程中非常重要的一个环节,现场可编程门阵列FPGA 具有高集成度、高效率、设计灵活以及功耗低等特点,FPGA 以其特有的复杂硬件逻辑控制能力与实时性、同步性被广泛应用到数据采集存储系统中[1 - 2]。本设计提出了一种基于FPGA 的多通道数据采集电路的设计方法。主要用来获取飞行器在飞行过程中的各种飞行参数,供其降落后回收原始数据,通过上位机软件在PC 机中读取飞行原始数据并实现原始数据的拆分以及绘图,供试验后进行数据分析,从而对飞行器的各项性能进行评估和验证。

1 硬件电路设计 1. 1 硬件电路的功能

该电路完成记录仪的采集功能,采集一路直流电压信号和6 路振动传感器信号,具体指标如下:

( 1) 直流电压: 测量范围: 0 ~ 100V; 精度: 1%; 采样率: 50kHz。

( 2) 振动传感器信号: 测量范围: ± 10g; 精度:1%; 采样率: 10kHz。

另外,该电路完成与上位机之间的通信,控制整个记录仪的工作状态。通过配套的上位机软件对记录仪下发各种命令,并将转换存储到flash 中的数字信号上传到上位机供分析。

1. 2 硬件电路的原理

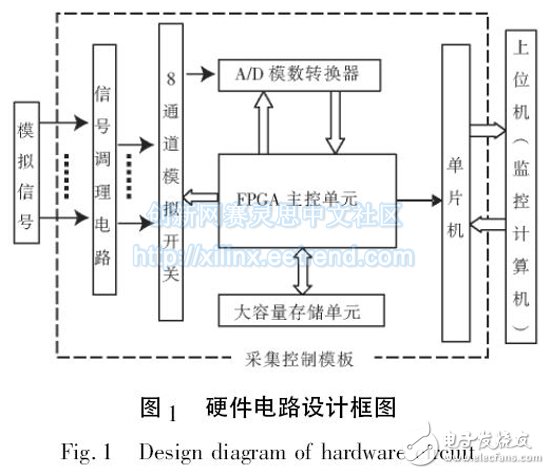

电路工作框图如图1 所示,待采集模拟信号经前级调理电路跟随调理后,主控制器FPGA 控制模拟开

关切换通道,实现了对6 路传感器振动模拟量以及1路直流电压的循环采集,FPGA 控制模数转换器AD7667,将采集到的模拟信号转换为数字信号并写入flash 存储器。试验后,通过USB2. 0 接口连接到上位机,用上位机软件对单片机发送读数命令,将flash 存储器中的数据读到上位机显示并处理分析。图1 中虚线部分为多通道采集控制模块。

对于一个复杂的系统,其功能具有多样化,一般要求硬件设计采用功能模块化的设计方法。把一个系统根据其功能的不同分解成多个模块,各模块具有相对独立性,而局部范围之间存在一定联系,有助于系统设计、调试以及维护,又易于功能的扩展[3]。该电路设计过程中,主要功能模块有采集记录功能模块和USB 接口模块。其中,采集记录模块是整个电路的核心,主要任务是采集待测信号、上传数据和控制其它电路。

2. 1 采集记录模块

2. 1. 1 采集模块设计

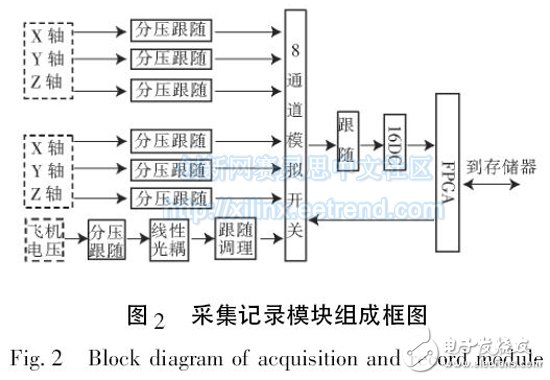

采集记录模块主要完成2 个三轴振动传感器( 共6 路) 和1 路直流电压信号的采样、编帧和记录,原理框图如图2 所示。

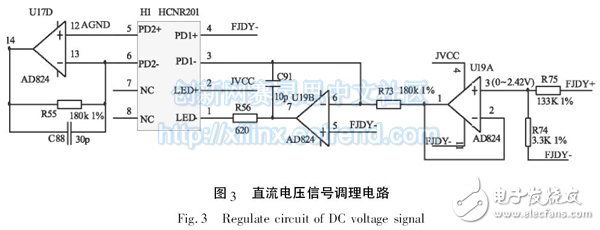

直流电压信号的测量范围为0 ~ 100V,跟随前需要进行分压,将输入芯片AD824 的电压控制在0 ~3V,并用线性光耦HCNR201 进行电气隔离,最后将电压范围调理到模拟开关ADG708 的模拟输入电压范围0 ~ 5V。调理电路如图3 所示。

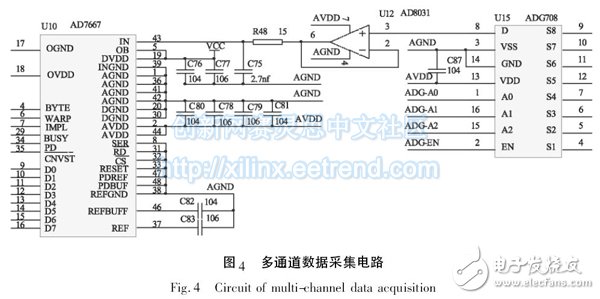

6 路传感器信号进入电路后,经过放大器AD824跟随调理输出的信号与调理后的直流信号一起进入模拟电子开关ADG708,ADG708 由FPGA 控制,A0、A1、A2 地址线决定选择一路信号输出,输出信号经AD8031 跟随后,增加了驱动能力,被AD7667 采样。采样字长为16 位,采集编帧后的数据存储到flash 存储器。采集电路设计如图4 所示。

2. 1. 2 AD7667 模块

AD7667 很容易被驱动,在本电路设计中采用AD8031 作为驱动器来增强信号的驱动能力,输出的信号被送入AD7667 进行转换。R48、C75 等阻容值采用AD7667 推荐值。

FPGA 控制AD7667,进入采集状态后,先启动AD7667 转换,转换完成后,以并行方式输出数据。在硬件电路设计上,为节约FPGA 的I /O 资源,降低硬件成本,转换得到的16 位的高精度数据以高8 位( byte = 1) 和低8 位( byte = 0) 分时从AD7667 的AD[7: 0]输出[4]。

2. 1. 3 FPGA 模块

该电路设计采用的FPGA 是XC2S400,该芯片有丰富的输入输出管脚和宏单元,通过VHDL 语言编程实现硬件逻辑功能,可以反复修改和擦除。

为了克服数据写入FPGA 和读出的速率不一致,此电路在FPGA 内部构建容量为2kB 的FIFO存储器,具有数据缓冲的功能[4 - 5]。实际调试过程中得到,2kB 容量的大小远远大于该时段内所能送来的最多数据量,这样就避免了溢出而造成的数据丢失。

FPGA 控制电路采集模拟信号,经过模数转换器转换后得到连续的数字信号,并将其写入FIFO 缓存中。FPGA 实时检测缓存器FIFO 的半满信号,每检测到该信号有效后,才开始从缓存器中读取数据并转发到flash 存储器,当读数速率较快并检测到FIFO半满信号无效时,停止读数。这样重复 *** 作,实现数据的连续采集[6 - 8]。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)