SMC主机接口模块可轻松将通过Synphony模型编译器创建的设计集成在赛灵思嵌入式平台中。

Synphony模型编译器(SMC)是一款Synphony提供的、基于模型的工具,其可综合在Simulink®及MATLAB®中创建的设计,从而可为ASIC和FPGA目标应用生成优化的RTL。SMC包含一个综合而全面的高级模型库,可在Simulink环境中创建数学、信号处理及通信设计。该库可在高级模型设计环境中简化定浮点单速率或多速率算法的捕获及功能调试。SMC RTL生成引擎可使用这些经过验证的模型自动创建RTL,为占位面积、性能、功耗以及吞吐量利弊权衡实现多架构的硬件实施及快速探索。SMC的高级综合引擎采用顶级设计以及MATLAB语言输入,可生成针对所选硬件目标而优化的RTL。此外,SMC还可针对设计自动生成一个RTL测试平台,并配以比特及周期高精度的C模型与SystemC封装程序,可在SystemC仿真环境中实现对所生成硬件的验证。

在许多应用中,设计人员通过创建外设来执行一些信号处理功能,并必须通过主机处理器(例如赛灵思 MicroBlaze™软处理器内核)来配置该外设。主机处理器通常采用标准总线接口(例如AMBA® AXI4或AXI4-Lite)连接外设。SMC库包括主机接口模块,其可来实现主机处理器的从接口。该主机接口模块不仅支持AXI4-Lite、APB、通用接口以及Avalon-MM总线接口协议标准,而且还可通过实现必要的内存映射的寄存器来配置SMC设计,其中包括FIR滤波器系数、数控振荡器(NCO)的频率与相位设置以及各种长度FFT模块的FFT长度。此外,该主机接口模块在实现内存映射的控制寄存器时可以采用任意需要的采样频率,可以与总线接口时钟异步。您可在主机接口模块的UI中指定总线接口及存储器映射设置。设计人员可使用主机接口模块将SMC设计连接至总线互联或者总线主控。

现在我们来详细了解一下,如何将通过SMC主机接口模块设计的外设导入并集成到赛灵思嵌入式开发套件(EDK)项目中。此外,我们还将考证如何仿真通过标准总线互连连接的从MicroBlaze主机处理器到外设的AXI4-Lite总线的数据传输。该过程有四个主要步骤:

1. 使用IP、主机接口模块以及SMC RTL生成引擎在Simulink中创建外设,为设计生成优化的RTL实施方案;

2. 将该外设导入赛灵思EDK工程,并将其与余下的设计集成;

3. 在SDK中开发软件应用;

4. 生成RTL并对其进行仿真,以检查软硬件功能是否正确。

第1步:使用SMC库创建外设

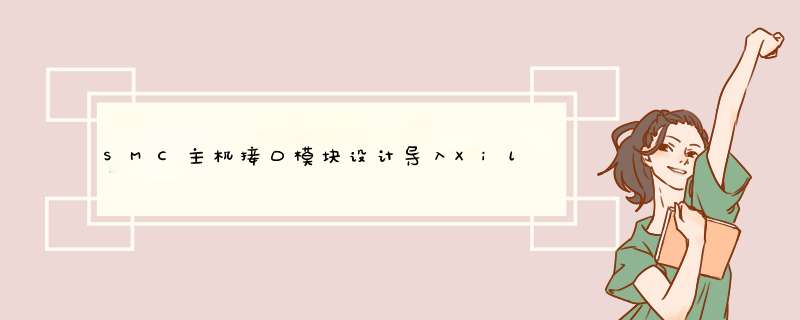

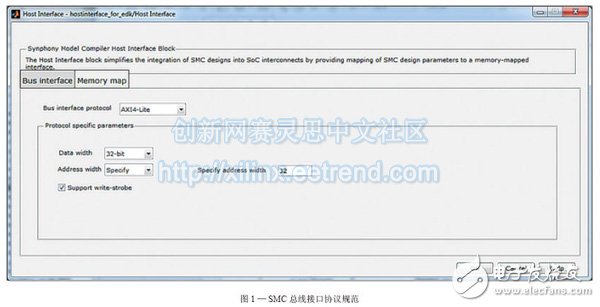

您要做的第一件事是使用SMC库模块创建外设的算法实施,并验证功能性。然后根据两个因素配置SMC主机接口模块:算法部分的配置数据(其可定义存存储器映射参数)与系统的互联总线协议(其可定义总线接口参数)。然后将主机接口模块与外设算法部分联系起来。主机接口模块的一些参数(例如总线互连、地址宽度与基址)将取决于您的目标平台。例如,我们选择赛灵思Virtex®-7 FPGA作为平台,并选择AXI4-Lite作为总线接口。该平台对每个外设的地址宽度、基址以及地址空间都有一定的限制。地址宽度必须为32位,而基址必须为4K字节的倍数,最小可用地址空间为4K字节。图1和图2是总线接口协议及存储器映射如何使用主机接口模块进行配置的视图。

为了便于集成,虽然不是强制性的,但也强烈推荐SMC模型中的总线接口端口遵循赛灵思EDK要求的命名惯例。请为标准AXI4-Lite接口信号名称添加“S_AXI_”。例如,AXI地址编写通道(AWADDR)的地址信号应该命名为S_AXI_AWADDR。如果信号不遵循AXI4-Lite的命名惯例,则在外设导入赛灵思EDK时就有可能将端口名称映射到AXI4-Lite信号名称上。另外,Simulink模型名称中不要使用大写字母,因为EDK不支持其名称中带有大写字母的外设。

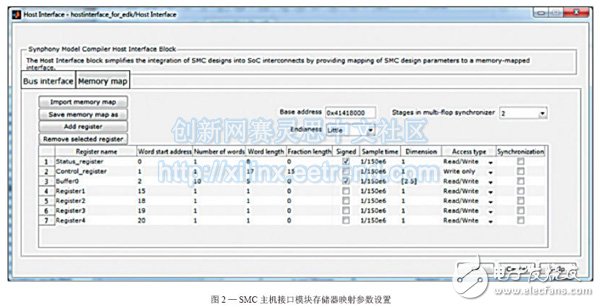

添加、配置和连接主机接口模块后,就可使用SMC的RTL生成引擎为外设生成RTL。请在SMC UI中指定目标设备、实施参数和优化限制,以促使RTL生成引擎为目标设备生成优化的硬件。在SMC生成的顶级RTL中添加两个虚拟参数(顶层RTL一般为VHDL),命名为:“C_BASEADDR”和“C_HIGHADDR”。根据IP要求将其默认值分配给存储器映射空间的基址和存储器映射空间的最大地址。这一步必需确保EDK可识别外设的存储器映射地址空间。SMC生成型设计的顶级Verilog RTL的实例如下所示,有两个参数需要高亮显示。

为了便于集成,虽然不是强制性的,但也强烈推荐SMC模型中的总线接口端口遵循赛灵思EDK要求的命名惯例。

第2步:将外设导入赛灵思EDK并对其进行集成

下一步是将外设硬件导入EDK的赛灵思Platform Studio(XPS),并在系统中进行必要的连接(总线接口端口以及功能端口)。在本示例中,我们已经创建了具有MicroBlaze处理器的基本系统、用于存储可执行软件的模块RAM (BRAM)、本地存储器总线(LMB)、AXI4-Lite互连以及MicroBlaze调试模块。

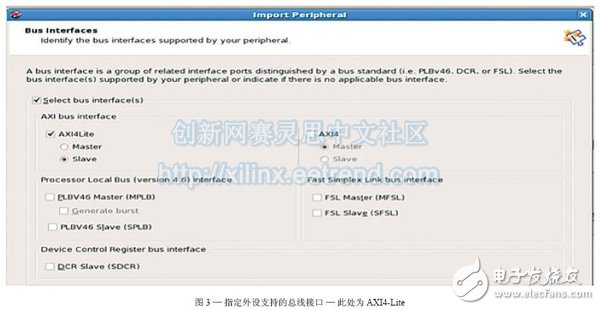

在XPS GUI的硬件目录下选择“创建或导入外设”选项。这将打开创建并导入外设向导。在该向导中选择“导入现有外设”选项。然后指定外设的存储路径、设计名称以及文件类型(HDL)。现在添加所有SMC生成的RTL文件。成功编译RTL之后,您需要识别外设支持的总线接口,即AXI4-Lite从接口,如图3所示。

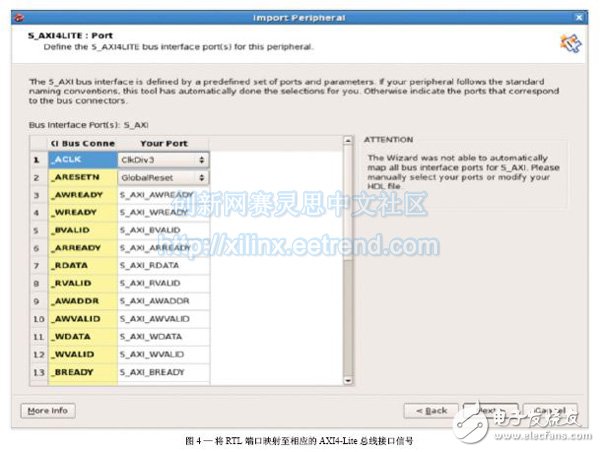

在向导的下一个页面中选择外设的AXI4-Lite端口,并将其映射到标准AXI4-Lite端口上,以便EDK能够连接总线接口。如果SMC模型中定义的总线接口端口名称与标准总线端口名称相匹配,则EDK将自动映射端口(参见图4)。

如果端口名称不匹配,则可能要覆盖自动映射,如AXI4-Lite时钟(Clk-Div3)和复位(GlobalReset)信号所示。

然后,按照第一步中插入RTL的C_BASEADDR和C_HIGHADDR参数,指定寄存器空间基址和高位地址。请取消选择存储器空间选项,因为主机接口模块具有可寻址的配置寄存器空间。但是在下个页面中要保持RTL参数的默认属性不变,以确保与主机接口模块中指定的参数一致。

下个页面的标题为“端口属性”。在这里,您必须指定时钟属性,或者所有其它时钟上的复位或设计中的复位。请点击下个页面中的“完成”,添加外设至XPS项目。SMC外设现已成功导入XPS。您可通过查看

/pcores文件夹(XPS使用外设名称在此创建一个目录)验证是否成功。浏览该目录,检查RTL文件是否正确导入。

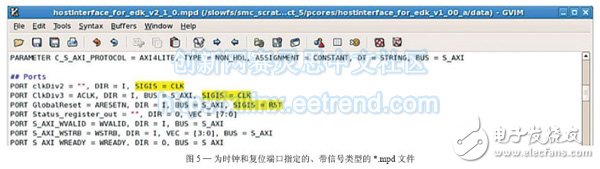

此外,XPS还将创建一个与HDL目录并列的目录,名为“数据”。该数据目录包含微处理器外设描述(*.mpd)文件以及相关外设参数及其端口信息。查看SIGIS = CLK和SIGIS = RST参数是否已在时钟及复位端口上定义。如果没有定义,则需要编辑*.mpd文件并手动添加定义。图5是添加了这些参数的文件实例。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)