通常基于传统处理器的C是串行执行,本文介绍Xilinx Vivado-HLS基于FPGA与传统处理器对C编译比较,差别。对传统软件工程师看来C是串行执行,本文将有助于软件工程师理解Vviado-HLS基于Xilinx FPGA对C的解析,综合原理。

1. Vivado-HLS FPGA并行与处理器架构

与处理器架构相比,FPGA结构具有更高的并行。Vivado-HLS对软件C程序编译时与处理器编译是不一样的执行机制。

2. Vivado-HLS FPGA与处理器程序指令执行

对于处理器, 程序执行以顺序指令, 如GC++,它将C/C++算法转换成assembly语言。

如

c = a + b

处理器将其转换成assembly代码如下:

LD a, $R1

LD b, $R2

ADD $R1, $R2, $R3

ST $R3 c

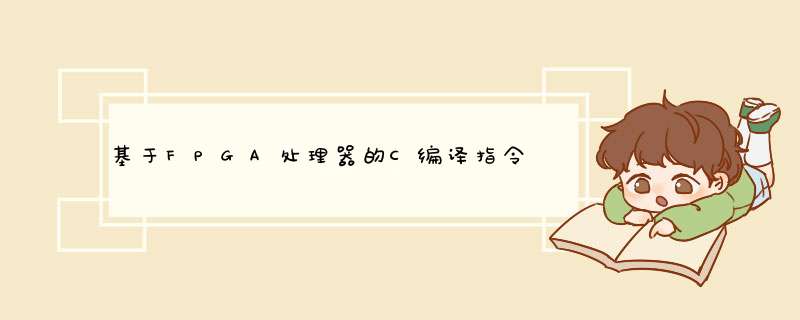

由此可见,对处理器简单的加法运算,都将需多个assembly指令集来完成。如下图所示分别是基于处理器的单一,及多指令执行单元。

上述c = a + b运算处理latency受限于数据a,b所存放的位置,如DDR,还是hard drive。

Vivado-HLS编译器是被用于将软件C/C++转换成RTL,由于FPGA是完全并行处理,转换不受限于指令的cache及内存空间。

如上例c = a + b, Vivado-HLS将其综合成一些LUT来实现。

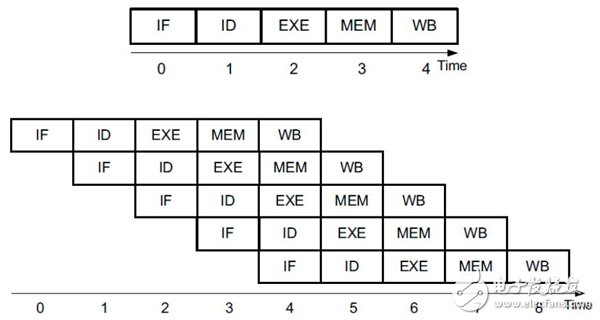

Vivado-HLS面向FPGA编译指令处理如下图所示,为完全并行。

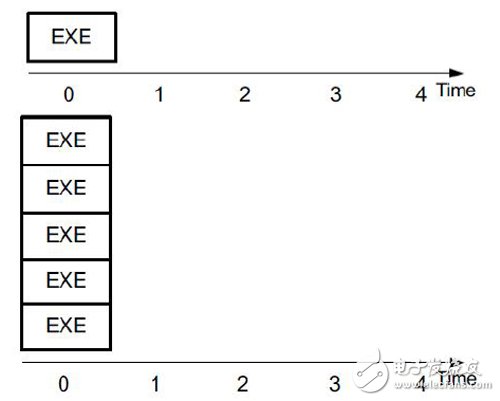

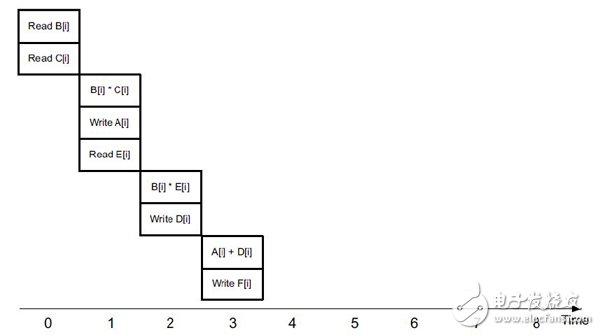

下面看多个运算的例子:

A[i] = B[i] * C[i];

D[i] = B[i] * E[i];

F[i] = A[i] * D[i];

对处理器将使用如下纯串行执行。因为数组 A, B, C, D, E, F被存在一个单一存储空间,所以每次只能 *** 作一个数据。

然而,对Vivao-HLS检测到这些存储并且对每个数组生成了独立的memory bank, 从而使得对数组B, C的 *** 作可以同时并行进行。

对Vivado-HLS FPGA将默认使用如下方式执行

下面再看对loop运算。

for (i=0; i<10; i++)

{

A = A + B[i] * C[i];

}

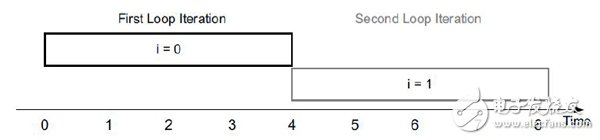

处理器对loop iteraTIon的scheduling如下图所示。 串行实现,第一次loop iteraTIon结束才开始第二次loop iteraTIon。

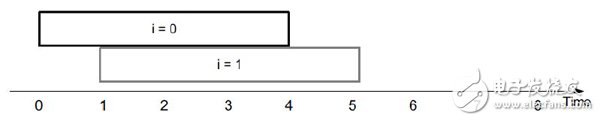

Vivado-HLS基于FPGA对loop iteraTIon的scheduling如下图所示。 不受限于第一次loop iteration结束才开始第二次loop iteration。从而可以并行实现II=1。在第一次loop的运算结束后就可以开始第二次loop的运算。

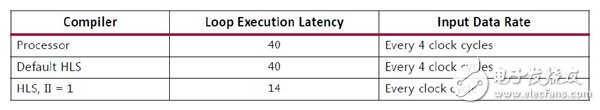

当然有时为了更小的FPGA资源,Vivado-HLS也可以综合成与处理器类似的串行实现结构。总结如下表所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)