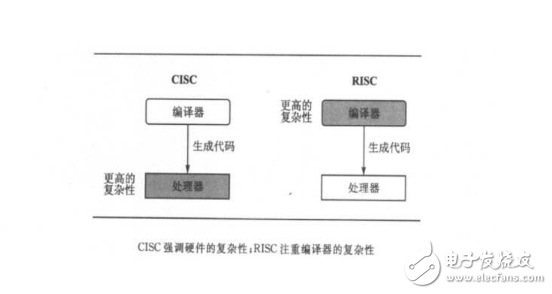

指令的强弱是CPU的重要指标,指令集是提高微处理器效率的最有效工具之一。从现阶段的主流体系结构讲,指令集可分为复杂指令集(CISC)和精简指令集(RISC)两部分。相应的,微处理随着微指令的复杂度也可分为CISC及RISC这两类。

复杂指令集计算机(CISC)长期来,计算机性能的提高往往是通过增加硬件的复杂性来获得.随着集成电路技术.特别是VLSI(超大规模集成电路)技术的迅速发展,为了软件编程方便和提高程序的运行速度,硬件工程师采用的办法是不断增加可实现复杂功能的指令和多种灵活的编址方式.甚至某些指令可支持高级语言语句归类后的复杂 *** 作.至使硬件越来越复杂,造价也相应提高.为实现复杂 *** 作,微处理器除向程序员提供类似各种寄存器和机器指令功能外.还通过存于只读存贮器(ROM)中的微程序来实现其极强的功能 ,傲处理在分析每一条指令之后执行一系列初级指令运算来完成所需的功能,这种设计的型式被称为复杂指令集计算机(Complex InstrucTIon Set Computer-CISC)结构.一般CISC计算机所含的指令数目至少300条 以上,有的甚至超过500条.

采用复杂指令系统的计算机有着较强的处理高级语言的能力.这对提高计算机的性能是有益的.当计算机的设计沿着这条道路发展时.有些人没有随波逐流.他们回过头去看一看过去走过的道路,开始怀疑这种传统的做法:IBM公司没在纽约Yorktown的JhomasI.Wason研究中心于1975年组织力量研究指令系统的合理性问题.因为当时已感到,日趋庞杂的指令系统不但不易实现.而且还可能降低系统性能.1979年以帕特逊教授为首的一批科学家也开始在美国加册大学伯克莱分校开展这一研究.结果表明,CISC存在许多缺点.首先.在这种计算机中.各种指令的使用率相差悬殊:一个典型程序的运算过程所使用的80%指令.只占一个处理器指令系统的20%.事实上最频繁使用的指令是取、存和加这些最简单的指令.这样-来,长期致力于复杂指令系统的设计,实际上是在设计一种难得在实践中用得上的指令系统的处理器.同时.复杂的指令系统必然带来结构的复杂性.这不但增加了设计的时间与成本还容易造成设计失误.此外.尽管VLSI技术现在已达到很高的水平,但也很难把CISC的全部硬件做在一个芯片上,这也妨碍单片计算机的发展.在CISC中,许多复杂指令需要极复杂的 *** 作,这类指令多数是某种高级语言的直接翻版,因而通用性差.由于采用二级的微码执行方式,它也降低那些被频繁调用的简单指令系统的运行速度.因而.针对CISC的这些弊病.帕特逊等人提出了精简指令的设想即指令系统应当只包含那些使用频率很高的少量指令.并提供一些必要的指令以支持 *** 作系统和高级语言.按照这个原则发展而成的计算机被称为精简指令集计算机(Reduced InstrucTIon Set Computer-RISC)结构.简称RISC.

优点:能够有效缩短新指令的微代码设计时间,允许设计师实现CISC体系机器的向上相容。新的系统可以使用一个包含早期系统的指令超集合,也就可以使用较早电脑上使用的相同软体。另外微程式指令的格式与高阶语言相匹配,因而编译器并不一定要重新编写。

缺点:指令集以及晶片的设计比上一代产品更复杂,不同的指令,需要不同的时钟周期来完成,执行较慢的指令,将影响整台机器的执行效率。

RISC体系的优缺点优点:在使用相同的晶片技术和相同运行时钟下,RISC系统的运行速度将是CISC的2~4倍。由于RISC处理器的指令集是精简的,它的记忆体管理单元、浮点单元等都能设计在同一块晶片上。RISC处理器比相对应的CISC处理器设计更简单,所需要的时间将变得更短,并可以比CISC处理器应用更多先进的技术,开发更快的下一代处理器。

缺点:多指令的 *** 作使得程式开发者必须小心地选用合适的编译器,而且编写的代码量会变得非常大。另外就是RISC体系的处理器需要更快记忆体,这通常都集成于处理器内部,就是L1 Cache(一级缓存)。 综合上面所述,若要再进一步比较CISC与RISC之差异,可以由以下几点来进行分析:

1、指令的形成 CISC因指令复杂,故采微指令码控制单元的设计,而RISC的指令90%是由硬体直接完成,只有10%的指令是由软体以组合的方式完成,因此指令执行时间上RISC较短,但RISC所须ROM空间相对的比较大,至于RAM使用大小应该与程序的应用比较有关系。

2、定址模式 CISC的需要较多的定址模式,而RISC只有少数的定址模式,因此CPU在计算记忆体有效位址时,CISC占用的汇流排周期较多。

3、指令周期 CISC指令的格式长短不一,执行时的周期次数也不统一,而RISC结构刚好相反,故适合采用管线处理架构的设计,进而可以达到平均一周期完成一指令的方向努力。显然的,在设计上RISC较CISC简单,同时因为CISC的执行步骤过多,闲置的单元电路等待时间增长,不利于平行处理的设计,所以就效能而言RISC较CISC还是站了上风,但RISC因指令精简化后造成应用程式码变大,需要较大的程式记忆体空间,且存在指令种类较多等等的缺点。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)