随着我国汽车数量越来越多,现阶段的交通灯模式采用的是定时控制,由于车流量是随时变化的。当此时没有车通过,而相对的车要等到此方向的绿灯结束显示红灯才能通过,在时间和空间方面的应变性能较差,这样不仅浪费了时间,还使得相对方向的车辆造成“堵车”现象。要想解决城市的“大堵车”现象,改善原有的交通灯控制系统是很有必要的。

因此本文在EDA技术的基础上,利用FPGA的相关知识设计了交通灯控制系统,可以根据实际情况对灯亮时间进行自由调整,整个设计系统通过Max+PlusⅡ软件进行了模拟仿真,并下载到FPGA器件中进行硬件的调试,验证了设计的交通信号灯控制电路完全可以实现预定的功能,具有一定的实用性。

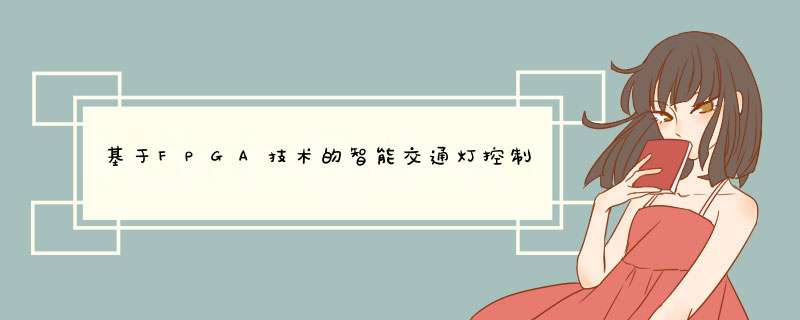

1、系统设计要求所设计的交通信号灯控制电路,主要适用于在两条干道汇合点形成的十字交叉路口,路口设计两组红绿灯分别对两个方向上的交通运行状态进行管理。交通灯的持续闪亮时间由键盘输入控制。灯亮时序如图1所示,当B方向的红灯亮时,A方向对应绿灯亮,由绿灯转换成红灯的过渡阶段黄灯亮,即B方向红灯亮的时间等于A方向绿灯和黄灯亮的时间之和。同理,当A方向的红灯变亮时,B方向的交通灯也遵循此规则。各干道上安装有数码管,以倒计时的形式显示本道各信号灯闪亮的时间。当出现特殊情况时,各方向上均亮红灯,倒计时停止。特殊运行状态结束后,控制器恢复原来的状态,继续运行。

图1 交 通灯闪亮时序图

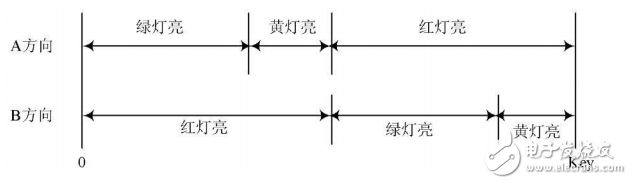

2、系统整体设计整个系统设计如图2所示,该系统主要由计数模块、控制模块、分频模块、分位模块以及显示电路构成。其中分频模块主要将系统输入的基准时钟信号转换为1Hz的激励信号,驱动计数模块和控制模块工作。控制模块根据计数器的计数情况对交通灯的亮灭及持续时间进行控制,并通过分位电路将灯亮时间以倒计时的形式通过数码管显示出来。图中Reset是复位信号,高电平有效,可以实现对计数器的异步清零。Hold为保持信号,当Hold为“1”,计数器暂停计数,表示出现特殊情况,各方向车辆都处于禁行状态。

图2交通灯控制系统模块图

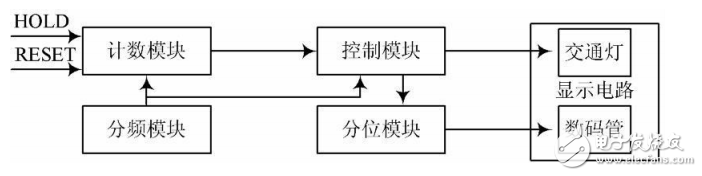

3、主要功能模块设计及仿真 3.1、计数模块设计计数模块主要实现累加循环计数,计数的最大值由键盘输入控制,输出的计数值为控制模块的灯控提供参考,计数器的主程序设计如下:

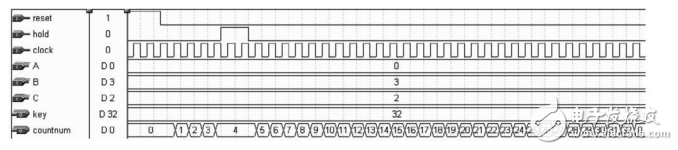

计数模块的仿真如图3所示,从图中可以看出,在时钟的驱动下,计数值不断自加,当计数值countnum等于键盘输入值32(key=32)时,计数返回到0,开始下一轮计数。当Hold检测到特殊情况时置`1‘,使计数器暂停计数。

图3计数模块仿真图

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)