智能交通灯是未来交通管理和车流量控制的发展方向,通过它可以更高效地对交通流进行限制、调整、疏导以改善通行效率、保障交通安全。

本设计通过综合目前各种交通灯的利弊,针对国内车辆种类多、随机性大、影响因素多等实际情况,提出1套完整的新型的基于视频监控的智能交通灯设计方案,该交通灯由视频采集、图像处理和控制模块组成,使用FPGA核心搭建专用高速视频采集模块,使用DSP处理器进行实时图像运算,通过图像算法提取车流量信息,最终结合模糊算法实现智能控制。

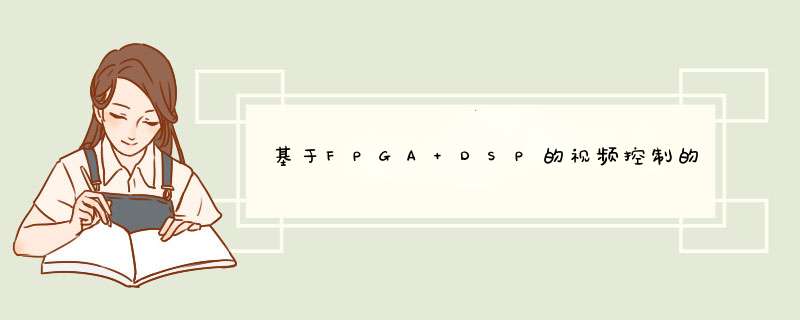

1、系统设计概述本系统完成了1种新型智能交通灯的设计,分为视频采集模块、视频分析模块和控制模块3部分,该系统把精简性、高效性、智能性和实用性进行了极大的集成。其系统结构框图如图1所示。视频采集模块以FPGA为核心,其高速并行的逻辑运算能力用于控制CMOS图像传感器的时序,并高效地存储和传输图像数据。

图1 系统结构

图像处理模块以DSP为核心,其丰富的硬件运算部件和加强的CPU多总线结构用来实时处理图像数据、分析交通流量状态。

控制模块主要由软件控制算法和DSP端口组成,这种预留的控制接口外接上不同的驱动电路即可控制不同规格的信号灯。

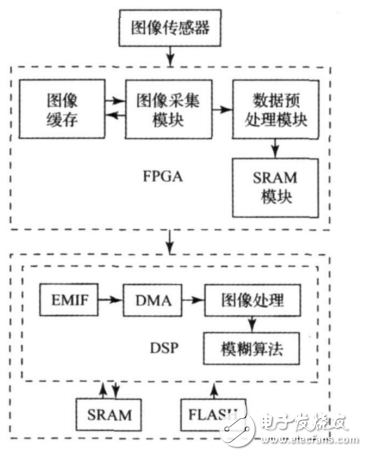

2、视频采集模块视频采集模块结构框图如图2所示。整个模块以FPGA为核心,外围扩展了CMOS图像传感器以及SDRAM存储器。

图2 视频采集模块结构

CMOS图像传感器OV7660的控制信号端和数据信号端直接与FPGA相连,通过近400个状态机精确完成OV7660各类指令的时序 *** 作。为了协调各模块的处理速率,采集过程以帧为单位对图像数据进行缓存,在SDRAM中开辟缓存空间存储当前帧和前一帧,在当前帧写入的时候进行前一帧读取。

DSP通过EMIF接口将FPGA模拟为外部SRAM进行图像帧的读取。使用定时器控制DMA将图像数据送入图像处理模块。

该信号链路精简高效,极大地发挥了FPGA时序控制优势,并通过优化缓存方案提高了数据传输的稳定性,为后端图像数据分析打下了坚实的基础。

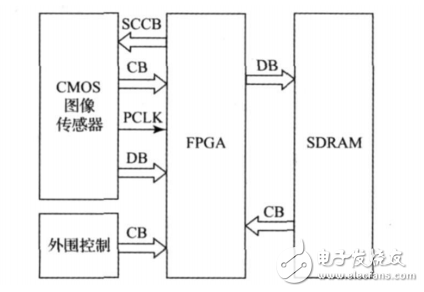

3、图像处理模块车流检测是智能交通系统的重要组成部分。通过视频图像来分析车流相比其他方式具有更大的优势,如成本低、系统精简、适应性强、扩展性强等。图像处理模块的主要目标是实现前景分离,即分离出静止的背景和相对运动的车辆。

传统的运动目标检测方法有光流法、帧间差分法和背景差分法。背景差分法是目前最常用的1种前景检测方法,背景差分法通过当前帧减去背景参考帧,然后对差分图像选择合适的阈值二值化后,就得到了运动目标。

背景差分法检测运动目标的效果在很大程度上取决于背景图像的质量。背景图像会随着光照和其他因素而变动,背景差分法的关键在于找到1个背景模型的自适应更新算法。本系统采用均值法获取初始背景图像,利用卡尔曼滤波原理建立背景模型,OTSU算法进行图像的二值化分割。图像处理模块结构框图如图3所示。

图3 视频图像处理流程

3.1、帧灰度化DSP从双口RAM中读到16位RGB565格式的彩色图像数据,为了提高图像处理的速度同时保留图像的大部分细节,可以提取图像中的亮度信息,将图像转换为YUV格式。其中亮度信息:

Y=0.299xR+0.587xG+0.114xB

处理效果如图4(b)所示。

3.2、去噪摄像头采集到的原始图像通常包含椒盐噪声和白噪声。椒盐噪声是由传感器,传输信道等引起的噪点,白噪声是频率意义上的随机信号干扰,服从高斯分布。为了提高后续处理效果,必须对原始图像进行去噪处理。去噪 *** 作同时会一定程度降低图像质量,所以在方法选择上应适度权衡。

本系统采用3x3滑动窗口中值滤波进行去噪处理,其去噪效果明显且能较好保存图像边缘。虽然中值滤波执行效率一般,但经优化后对实时性影响甚微。

将3x3的数据序列分为3组分别排序,获得最大值组、中值组、最小值组,然后在最大值组的最小值、中值组的中值和最小值组的最大值3个值中取中值,结果即为序列的中值。处理效果如图4(c)所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)