在这篇文章中,笔者将介绍各种不同型态的 3D IC 技术,由最简易的开始到目前最先进的解决方案。不过当我们开始探讨3D IC,第一件事情就是要先问自己:「我们是想要透过3D达成什么目的?」这个问题并不无厘头,因为3D对不同的人来说可能代表的东西也不同。

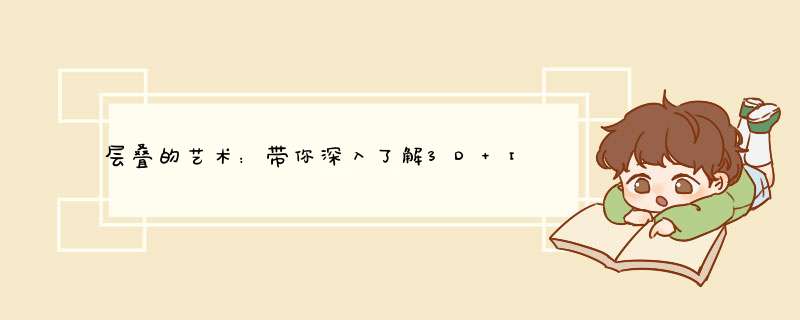

举例来说,3D IC的初期型态之一(目前仍应用于一些特定领域),是将功能相同的裸晶──如记忆体──结合在一起,形成3D堆叠,再由两侧绕线连结,最后以系统级封装(system-in-package,SiP)的外观呈现。虽然下面的图里画的晶片堆叠看起来有点高瘦也不太美丽,但其实每颗裸晶厚度只有0.7mm (甚至可研磨至厚度仅0.2mm)。

从两侧连结的3D晶片堆叠

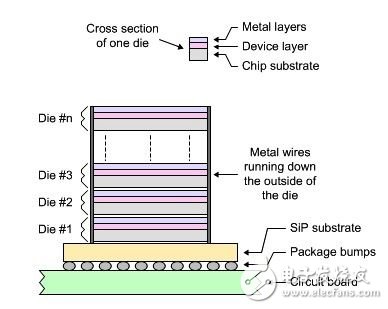

另一种常见的方式是在采用覆晶(flip-chip)技术的SiP基板上先放一颗裸晶,然后再将第二颗裸晶以打线接合方式放在最顶端,如下图;但这两种技术虽然都非常高明,在笔者的心目中还达不到 3D IC 的等级。

简易的 3D IC / SiP

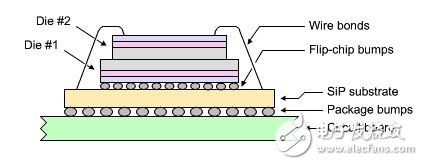

传统2D IC与SiP

接着的讨论如果我们不谨慎一些,事情可能就会变得有些棘手,所以让我们一步步来;首先,退回去想想在传统的2D IC与SiP阶段,裸晶与或是晶粒(dice)是放置在单一平面的封装内。传统2D IC的配置方法常是如下图:

传统2D IC与SiP

为了简单起见,我们在上图的SiP只放了两颗晶粒,但当然实际情况也可能是有更多颗的;此外在图中我们是假设晶粒是以覆晶技术(有时候也可能用打线)放置在SiP基板上。在这个例子里,覆晶锡铅凸块(solder bump)的直径约只有100μm。

而我们也假设该SiP基板是一种层压板(laminate),那是一种小型、精细的印刷电路板,有铜轨(track)与包含一定数量轨道层(tracking layer)的铜通孔。这种形式的SiP技术实在令人印象深刻,SiP基板上的轨道尺寸比矽晶粒上的轨道要大得多,这种尺寸上的差异会影响性能与功耗。此外SiP基板上尺寸较大的轨道会导致绕线壅塞,使得裸晶与裸晶之间的连结数量受限。

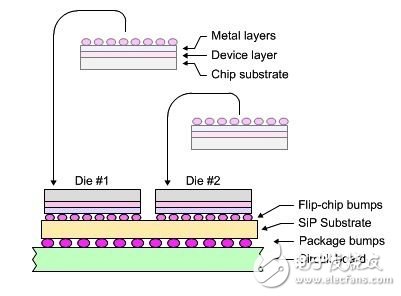

结合TSV的被动上主动式3D IC /SiP

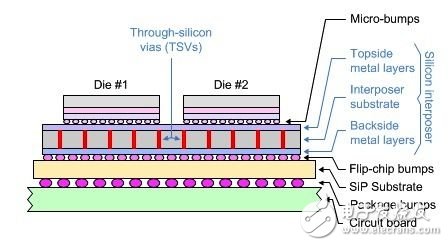

再往上把复杂度提升一个等级,就是在SiP基板与晶粒之间放置矽中介层(interposer),如下图所示,矽中介层具备矽穿孔(TSV),连结上方与下方表面的金属层。有人将这种技术称为2.5D,因为矽中介层算是被动元件,也就是不承载像电晶体那样的主动元件;但这种方式也并非罕见,可称之为被动上的主动式(acTIve-on-passive) 3D IC /SiP。

结合TSV的被动上主动式3D IC/SiP

在这个例子里,晶粒以直径约10μm的微凸块与矽中介层接触,同时矽中介层以直径约100μm的常规覆晶凸块与SiP基板接触。矽中介层正面与背面金属层(两边都有可能是多层金属)上的轨道,是以与矽晶片上的轨道相同之制程所制作。

虽然上图里的矽中介层与晶粒看起来有点矮胖,但请注意它不是等比例画的,实际上晶粒与矽中介层的厚度只有0.2mm到0.7mm左右。Xilinx的Virtex-7 2000T 就是一款4颗FPGA晶粒连结矽中介层的元件,支援相邻晶粒之间约达1万的连结线。

被动上的主动式3D IC / SiP 技术优点,在它是由传统2D IC / SiP 演进而来,在容量与性能方面有大幅的提升;该技术在良率上也有优势,因为要制作多个小型晶粒,会比制作单一大型晶粒来得简单。但其主要缺点则是要完成以上所有程序并不那么容易。

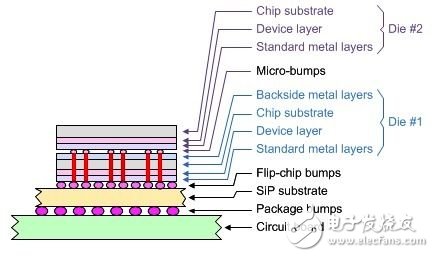

结合TSV的主动上主动式3D IC /SiP

再进一个等级的技术是主动上主动式(acTIve-on-acTIve) 3D IC / SiP,其中至少有一颗晶粒是与另一颗晶粒叠放在一起,下方的那颗是采用TSV技术,让上方的晶粒与下方晶粒、SiP基板通讯。如下图。因此举例来说,我们可能有一颗记忆体晶粒连着一颗逻辑晶粒,或是一颗类比/RF晶粒与一颗数位逻辑晶粒连再一起…等等。

采用TSV的简易主动上主动式3D IC / SiP

上图显示的是简单的配置法,可能在不久的将来,我们就能看到更多颗晶粒以TSV堆叠在一起,以及数群晶粒利用矽中介层相互连结,然后这些全部都在单一SiP封装中,如下图;这看起来可能有点像是纽约市的大楼群,但如我们先前一再强调,那些晶粒与矽中介层的厚度都只有0.2mm至0.7mm,整个封装会比你想像的小很多。

复杂度更高的3D IC / SiP

看了这么多 3D IC 技术,你可能好奇这个市场到底有多大?根据市场研究机构Yole Developpement的2012年报告,2011年采用TSV技术,以3D IC或3D-WLCSP形式制作的元件(包括CMOS影像感测器、环境光感测器、功率放大器、RF或MEMS惯性感测器等)市场规模约27亿美元,在整体半导体市场占据约9%,而估计到2017年将成长至400亿美元。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)