半导体制程工艺上,英特尔要是说第二,那没人敢说第一。晶圆制造这个圈子,英特尔毫无疑问处于第一流,其他厂商包括IBM,英飞凌,NEC,意法半导体以及东芝等公司,以及目前半导体代工行业的老大老二老三——台积电、 GlobalFoundries、三星,统统都是二流。

说这么绝对可能有人不服,小编举最近的一个例子,英特尔仅仅破一次例为美国芯片制造商Altera代工首个四核64位ARM Cortex-A53处理器,就引发了业界一片惊叹。

为了让大家一窥 Intel在半导体制造工艺上的牛逼,笔者选取数月前参加Intel新品交流会后,印象深刻的45nm以下HKMG的成型工艺来做探讨。

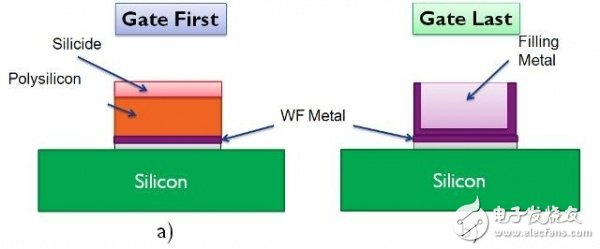

随着晶体管尺寸的不断缩小,HKMG(high-k绝缘层+金属栅极)技术几乎已经成为45nm以下级别制程的必备技术。不过在制作HKMG结构晶体管的 工艺方面,业内却存在两大各自固执己见的不同阵营,以IBM为代表的前栅极Gate-first工艺流派和以Intel为代表的后栅极Gate-last 工艺流派。更准确点说,在步入HKMG时代之初,只有Intel 和其他所有半导体企业之别。

前栅极和后栅极工艺实现HKMG结构,在技术上有什么差别,请看这段引用:

Gate- last是用于制作金属栅极结构的一种工艺技术,这种技术的特点是在对硅片进行漏/源区离子注入 *** 作以及随后的高温退火工步完成之后再形成金属栅极;与此相对的是Gate-first工艺,这种工艺的特点是在对硅片进行漏/源区离子注入 *** 作以及随后的退火工步完成之前便生成金属栅极。Gate-last工艺的难点则在于工艺较复杂,芯片的管芯密度同等条件下要比Gate-first工艺低,需要设计方积极配合修改电路设计才可以达到与Gate-first 工艺相同的管芯密度级别。采用Gate-first工艺制作HKMG的劣势,是用来制作high-k绝缘层和制作金属栅极的材料必须经受漏源极退火工步的高温,会导致PMOS管Vt门限电压的上升,这样会影响了管子的性能。

如果对这段不太理解的童鞋,只需要记住一点:后栅极成型HKMG技术制造的芯片,功耗更低、漏电更少,高频(即高性能)运行状态也更稳定;但是生产制造技术复杂、良品率低、初期很难大规模量产;(在没有采用3D晶体管结构前)管芯密度低,对晶圆的利用不够经济;真正实用时,还需要用户层面的配合,即客户厂商根据需求配合修改电路设计。

45nm以下必要的HKMG技术中Gate-first/Gate-last成型工艺各有优劣,Intel追求未来的性能增长选择Gate-last,其他厂商则选择整体难度较小、眼下更容易实用的Gate-first,经过几年发展后,情况如何呢?

先看Gate-first,下面这段话引用自英特尔中国技术发言人洪力的评价:

28 纳米去年TSMC(台积电)刚刚用到所谓后栅极工艺,英特尔从45纳米开始用后栅工艺,那是4年以前的事。这个时候功耗就来的小,那个时候我们出来包括 IBM那些所有的人出来说英特尔宣布做后栅工艺的时候,不可能达到经济利益上的量产,因为太难做了,英特尔做出来了。为什么后栅很重要,当处理器运算的频率高的时候,你的功耗就会很大,这部分做起来很不容易。所以你会看到去年很长时间都讲到产能不足的问题,现在TSMC有了,三星的 28纳米还是前栅工艺的。到22纳米的时候我们其实已经开始做三维晶体管,这是晶体管的一个创新,栅极起来了。那样的分布方式使得它的性能和功耗、密度都会有一个更大的提高,你去看一看TSMC的3D的晶体管是2015年开始量产,可以看到中间差多远,三年半的时间。此28纳米和彼22纳米不是一回事。还有一些厂商说还有14纳米更小的,这跟做逻辑的不是一回事,所以英特尔领先是按代来衡量的,是一代还是两代。

再看看Gate-last,这是台积电研发部门高级副总裁蒋尚义从Gate-first阵营转向Gate-last阵营时说的话:

和 20年前一样,我们现在又遇到了如何控制Vt(管子门限电压)的难题。如今的Gate-first+HKMG工艺同样存在很难控制管子Vt电压的问题。尽管厂商可以在管子的上覆层(capping layer)上想办法对这种缺陷进行补偿,不过这种方案“极其复杂和困难程度相当高”Gate-last工艺当然也存在一些局限性。比如这种工艺制出的管子结构很难实现平整化。不过如果设计方的Layout团队能够在电路设计方面做出一些改动,那么就可以克服这个问题,使Gate-last工艺制作出来的芯片的管芯密度与Gate-first工艺相近。在我们采用后栅极工艺的时候,有的客户一开始抱怨连连,曾一度表示如果采用这种新工艺,那么产品的管芯密度很难与Gate-first保持一致,不过经过我们多次面对面的商谈讨论,客户们已经完全接受了这种新的工艺。我相信目前仍坚守Gate-first阵营的厂商在22nm制程节点将被迫转向采用Gate-last工艺。我不是在批评他们,只是认为他们最终会改变观念的。除非他们能找到一种成本低,极具创意的方案来控制管子的门限电压,否则他们必然要转向Gate-last工艺。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)