什么让Red Pitaya在于其他设备相比中脱颖而出?这是因为它设计为通用的平台,透过“Bazaar”—一个在线入口类似智能手机的应用程序商店,可为不同用户配置。这篇文章探讨了如何透过较灵活的硬件和开放原始码的软件来实现。

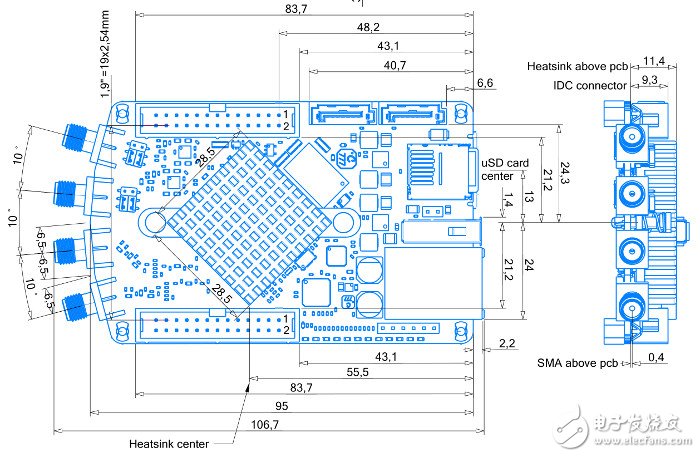

硬件平台的核心是一个包含了一个双核心的ARM处理器,接口设备和FPGA为一封包的Xilinx Zynq system-on-chip (SoC)。ARM和接口设备统称为“处理系统”(PS),并且提供给运行 *** 作系统和应用软件的计算机。此系统有512 MB的RAM,Micro SD卡用于储存,最多支持扩充达32 GB,也可以通过千兆位的以太网络和USB的UART端口来连接。

FPGA提供28000可程序化的RAM和DSP芯片。这是为了提供主要的ADCs和DACs接口,并且支持硬件方面的处理,加上常见的接口和扩充等。

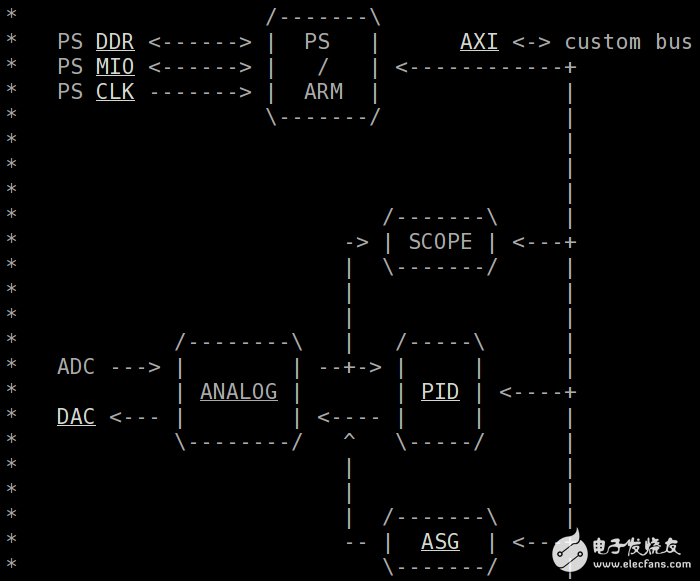

Red Pitaya的高速数字转换器提供两个模拟输入和两个模拟输出——125 MS / s的速度和14位分辨率,并且透过FPGA和AXI总线连接到PS。上图可以看到FPGA RTL模块文件中的一部分ASCII流程图,并且和Zynq外部引脚、PS、应用程序模块连接在一起。

一个模拟扩充连接器提供了四个低速模拟输入和四个低速模拟输出,每个在100 kS/s和12位分辨率。板子另一面还有类似的连接器,提供16个由FPGA GPIOs组成的数字扩充头。

菊炼板通过两个SATA连接器,每个皆提供两对差动对,并支持高达500 Mbps的数据传输速率。请注意, SATA并不支持驱动,连接器只是由于其性能和低成本的常用的缆线所组成,而常被使用。

软件

板子上面运行从Xilinx sources下载的Linux3.9.0版本,带有一个由BusyBox构成的ramdisk。接电源时,将从SD卡加载以下文件:

boot.bin:包含第一阶段的bootloader,FPGA image和U-Boot bootloader。

uImage: Linux 内核。

devicetree.dtb:Linux设备分支图(描述外围设备等)

uramdisk.image.gz:包含root文件系统的ramdisk

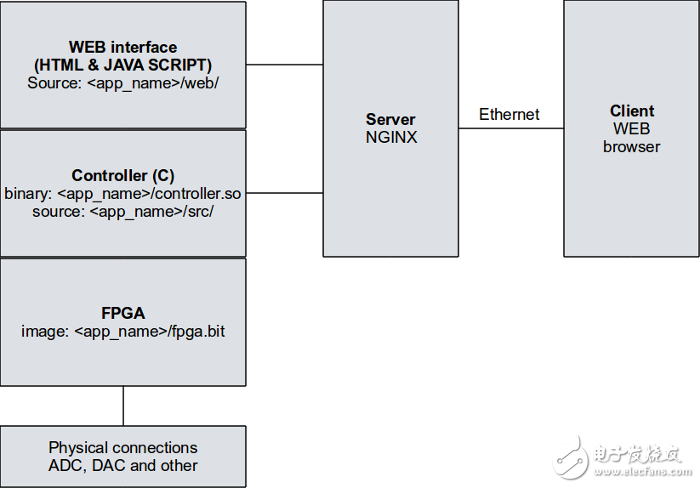

一旦启动了高效能和低内存的web服务器,nginx就启用了。这是用来提供HTML和JavaScript的网站应用程序给客户端浏览器。接着连接到一个控制器,一个服务器端Linux应用程序,这依次经由ADCs和DACs等接口接口连接到FPGA。所以,每个应用程序由三个部分组成:一个web用户界面,服务器端控制器和FPGA模块。

命令行工具同样可以使用,这些可以透过SSH远程执行,使诸如GNU Octave和Matlab的整合成为可能,并且对测试和除错是有用的。这些也是Linux二进制程序和在软件体系结构的控制器旁,通过这个接口连接到FPGA并且与ADCs和DACs相连接。目前已提供两种类似工具,分别为信号的产生和取样。

开发者

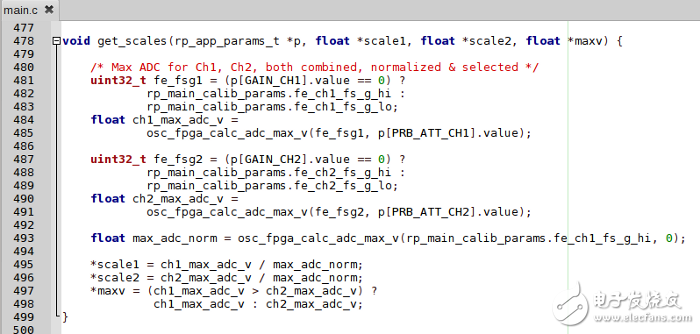

示波器应用控制器的部分main.c文件

RedPitaya GitHub 知识库包含的原始码:

FPGA设计资源 (/FPGA/)

Linux核心、U-boot、root文件系统 (/OS/)

Nginx和控制器模块加载程序等 (/Bazaar/)

Web应用(/ApplicaTIons/)

命令行工具(/Test/)

注意, *** 作系统子目录不包含完整的Linux和U-boot,他们是从其他地方复制,而不是只包含特定平台的补丁和配置等。

FPGA可以使用WebPack, Xilinx ISE或者Vivado设计软件生成比特流,而不是使用GUI。这些驱动使用执行脚本和命令行工具的makefile-based构建的系统。

Web应用程序,HTML和JavaScript代码可以使用文本编辑器进行编辑。控制器和命令行工具都是用C语言编写的,并且可以使用PC的ARM编译程序进行编译。和大多数Linux发行版相比,它只需要几个命令来安装一个ARM工具链。

应用程序必须被给予唯一的应用程序ID,放在一个同一名称的目录内,然后打包为ZIP文件,才能通过Bazaar来做发布。除了web应用程序和控制器,它还必须包含一个图标,和带有名字、文件和版本等的JSON文件。

目前所有应用程序使用相同的嵌入在boot.bin中的FPGA比特流。这对于许多新的应用领域将是足够的。然而,它也可以分发常见的比特流作为应用程序的一部分,实现修改和新的以FPGA为依据的DSP,并能够控制其他设备和透过GPIO与外部周边界面做连结。

结论使用可编辑Zynq SoC为整合数字转换器和实现硬件的信号处理的自定义I / O,提供了一个良好的解决方案。因为它是高度可配置的,如果你想利用其全部功能开发新的应用程序,可能要有一个学习曲线,。然而,许多新的应用程序就可以简单地按原样或相对较小的修改来使用现有的FPGA设计。

建立在Linux和web技术,很容易想象Red Pitaya可以定制和扩展许多不同的方式。例如,用于日志记录到本地或远程数据库,通过SNMP发送警报,或通过公共API整合在线服务。

最后, 除了在wiki上面提供文文件,同时提供结构良好的原始码,并且带有大量的评论和ASCII art diagrams,。所有的工作都是为了使初次使用这个平台的开发者能够更加容易运行。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)