目前,A/D转换器随着速度及精度的提高,价格愈趋昂贵,给实际应用带来困难。但在某些场合被测信号的变化是缓慢的,这时转换速度就不成为主要问题。此时,可以采用低速的双积分式A/D芯片,如ICL7135(国产型号5G7135)是4又1/2位,分辨率为1/40 000,精度相当于14位二进制的A/D转换器;MC14433(国产型号5G14433)是3丢位,分辨率为5/10 000。5G7135与5G14433都采用双斜率工作方式,所以具有很高的抗工频干扰能力。但其转换速率较低,为2~10次/秒。如果转换速率要求在20次/秒以上或更高,则无现成的双积分A/D转换集成电路。从原理上讲可以用积分器、比较器、计数器构成速度较高的高精度A/D,但由于受器件性能的限制,如电压比较器的有限增益和有限转换速率等,实现起来比较困难。兼顾价格与转换精度的另一种有效方法是,采用V/F技术构成高精度的A/D转换器。近几年由于集成电路技术的发展,V/F芯片价格下降,技术指标进一步提高,特别是单片式的V/F芯片在各行业中得到广泛的应用。AD650是高精度型的单片式V/F变换器,它与单片机结合可以构成分辨率高、转换速率高于20次/秒的A/D转换器。

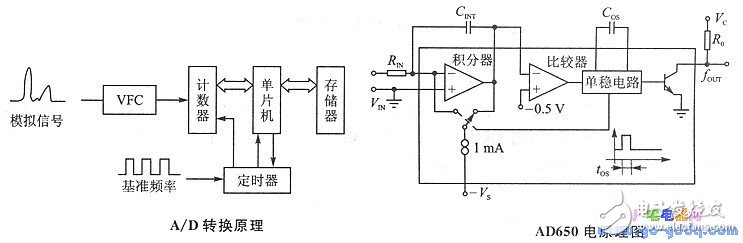

1.VFC与单片机的模/数转换的基本原理如图1所示,转换前,单片机首先对计数器及定时器清零,预置计数及定时初值;随后通过定时控制端及计数控制端,使定时器及计数器同时开始工作;到一定时间后,定时器溢出端发出信号,单片机检测到该信号后,停止计数器工作,并把计数结果送入存储器中。这样便完成了一次模/数转换。VFC输出的矩形波的频率与其输入电压成线性关系,计数器的计数值等于VFC输出频率乘以定时器时间,而定时器时间可以通过单片机来精确控制。所以此种方法的转换精度主要取决于VFC的精度。

2.AD650与单片机接口的硬件设计AD650是电荷平衡式单片V/F变换器,图2为其电原理图。

AD650的接线不很复杂,仅须选择4个元件的数值:输入电阻RIN、定时电容Cos、逻辑电阻Ro及积分电容CINT。下面介绍选取原则。

Ro:根据TTL逻辑电平,晶体管T在导通时约有0.4 V管压降。为保证有足够的负载能力,希望流过Ro的电流为8 mA。这样R。便近似为0.5 V/8 mA=62.5Ω,一般取1kΩ。如选1MHz为满量程频率,则必须采用500 Q左右的上拉电阻,以获得足够短的上升时间。

RIN与COs:这两个参数决定了满刻度频率及相适应的输入信号电压范围。RIN与Cos的关系是非线性的。满度频率为1 MHz、输入信号为0~10 V时,Cos可选51 pF,RIN为16.2 kΩ。

CINT:大多数情况下,CINT的最佳值按下式计算得出:

1 MHz时,CINT仍取1000 pF为宜。

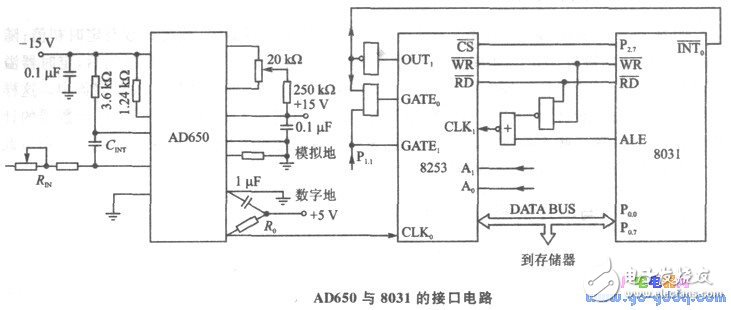

模/数转换所用的定时器及计数器选用Intel公司生产的8253芯片来实现。它内部有三个独立的可预置数的16位递减计数器。每个计数器都有一个时钟输入端CN、一个门控输入端GN、一个输出端ON。时钟输入端用于输入时钟脉冲或事件计数脉冲,计数器的值在时钟脉冲的下降沿变化,门控端可以送入控制或复位信号。计数器减到零时,由输出端送出标志信号。

图3为接线图,AD650的输出接8253计数器O的CN端,计数器1作定时器用。8253的数据线与8031的BUS直接相连,Ai、Ao接8031的地址锁存器74LS373的输出。存储器的分配采用线选法,即8253片选端CS(反相)接8031的P2.7端。由此可知,计数器0的地址为7FFCH,计数器1的地址为7FFDH,计数器地址为7FFEH,方式控制寄存器端口为7FFFH。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)