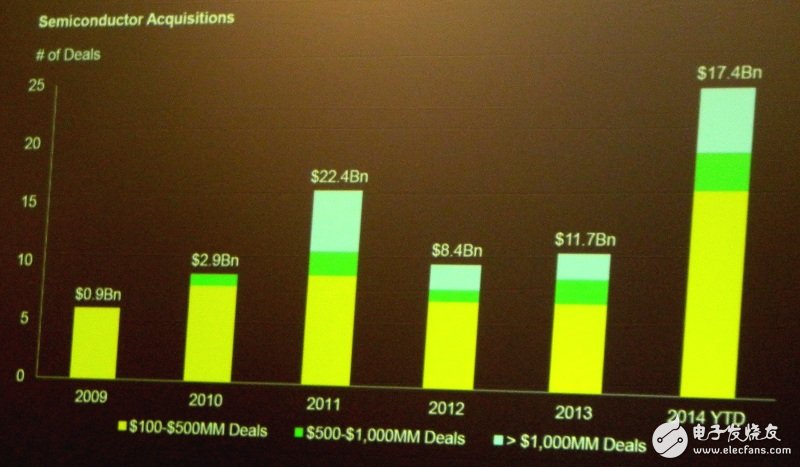

2014年S3S会议上,工程师共同分享了SOI材料的优势,亚阈值电压的设计新方案,单片3D集成以及今年的企业并购案。今年芯片行业一共有23起收购案,比前两年的总量还多。预计到年底,并购的总额将由174亿美元上升到30亿美元。

近几年并购案分析

芯片制造成本越来越高,工艺也越来越复杂,这已经潜在的促使了半导体厂商的合并。研发一颗28nm芯片需要3600万美元,而20nm芯片需要耗资5300万美元,16nm和14nm更是天价级别。

晶体管生产的费用正在不断的上升,这是不争的事实。但是,英特尔在9月宣称其14nm FinFET制程可降低生产陈本。

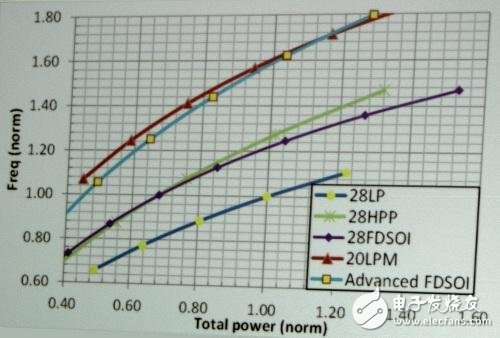

尽管14/16 nm FinFET技术是行业的主流趋势,超薄SOI制程依然存在相当的机会。

对于手机芯片来说,10nm和14nm FinFET技术价格太贵,近4-6年内都不会选择FinFET。而20nm SOI或许可满足手机芯片的价格问题。

另一方面,联发科高性能处理器技术总监Alice Wang对亚阈值区做案例了研究,这一目的是为了使芯片达到低功耗特性。

随着可穿戴设备的出现和其技术问题低功耗设计也是大势所趋,然而这给市场打来了极大的挑战。

目前,在两次会议上共同商讨的单片3D设计方案已经在最新的闪存中使用。CEA-LeTI和ST的研究人员利用单片3D集成技术代替节点缩放,这大大减少了研发的费用。EV Group和尼康的代表还分享了成键和定位系统技术,这一方面降低了目前3D芯片堆栈的成本另一面使其更简洁。

EV Group展示了200nm甚至更精确的定位系统将成为可能,尼康代表还指出EGA精密芯片键合方法可应用于未来的3D芯片制造,例如DRAM、MPU和图像传感器。

——电子发烧友网原创编译,转载请注明出处!

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)