引言

随着工艺技术的不断发展,高性能数字芯片中越来越广泛地采用高速存储器和多种总线标准,并需要提供多种电平标准的参考电压,这给接口电路的设计提出了挑战。设计支持高速通信、高覆盖性的电平标准,支持多种接口协议,可控延迟,并具备一定的工作速度、稳定性和高的驱动能力的可编程输入输出接口电路成为当务之急。基于以上分析,本文设计了一种多协议可编程输入输出接口中的输入接口电路,在用户配置基准电压和输入模式的情况下,可以支持多达10种的不同协议标准,并可以通过可编程延迟模块消除焊盘至芯片内部的保持时间,实现信号通路的同步性。

1 电路拓扑结构及协议分析

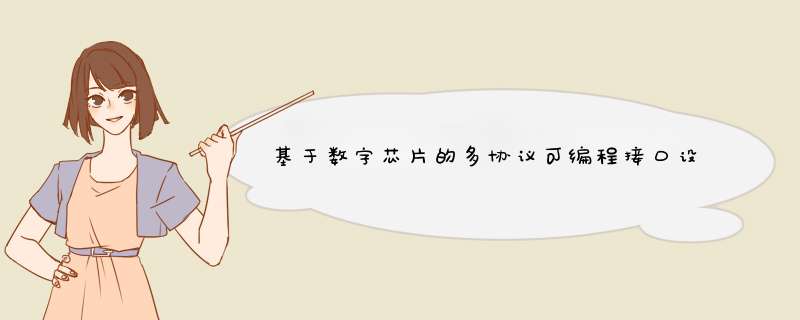

目前高性能数字芯片的输入输出接口模块(IOB)通常采用如图1所示的拓扑结构,它完整地提供了从管脚到芯片内部逻辑之问的连接。该结构主要由可编程输入缓冲、可编程输出缓冲、输入触发锁存器、输出触发器、可编程延迟及ESD保护构成,每个IOB控制一个引脚,它可被配置为输入、输出或双向I/O功能。当IOB控制的引脚被定义为输入时,通过该引脚的输入信号先送人可编程输入缓冲器。缓冲器的输出分成两路:一路可以直接送到多路选择器,经选择后输入芯片;另一路经可编程延迟模块延时几个纳秒(或者不经过延时直接输入),然后送到输入通路触发器,再送到数据选择器。通过编程控制数据选择器,且输入输出触发器都配有独立的时钟,可以任选采用上升沿或下降沿作为有效作用沿,从而达到对输入的可编程控制,提供不同的接口协议。

本工作重点是设计该模块中的可编程输入子模块电路,主要包括可编程延迟模块、可编程输入缓冲模块、ESD保护模块及输入触发锁存器、选择器等,设计目标是必须完成多种通用及高速输入标准协议的可编程选择。目前高集成度的接口协议称为JEDEC (joint electron device engineering council)标准。常见的输入输出接口标准定义在JEDEC8系列中。

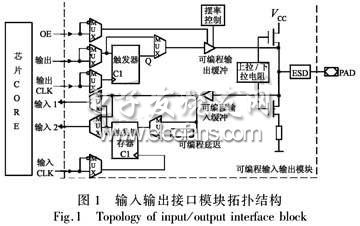

JEDEC定义了输入输出接口的电气性能,包括供电电压、输入最低高电平VIH、输出最高低电平VIL、输出最低高电平VOH、输出最高低电平VOL、最大电流驱动能力、输出摆率等,此外还需要根据特定的输入输出标准提供用于差分输入的用户自定义基准电压VREF。以频率较高的HSTL标准及较为通用的LVCMOS协议标准为例,其JEDEC定义的电气性能如表1所示。

可见,必须设计不同的输入缓冲模块为不同标准提供输入路径。HSTL协议摆幅电压较低,频率可达200 MHz,但不具备5 V电压耐压能力,且必须差分输入,需从外部提供0.75 V基准电压;LVCMOS协议电压较高,耐压能力强,为单端输入,可选用single-ended端至端输入缓冲器。根据表1中的9种不同协议特性,将其分为三组,通过不同的输入缓冲模块进行输入,分别进行编程控制,根据需要添加延迟量。模块电路结构如图2所示,其中编程控制点均未给出。

其中,低基准电压缓冲器完成较低基准电压的协议差分输入,包括HSTL/GTL/GTL+协议,基准电压分别为0.75、0.8、1.0 V;高基准电压缓冲器完成较高基准电压的协议差分输入,包括CTT/SSTL2/SSTL3协议,基准电压分别为1.5、1.25、1.5 V;单端输入缓冲器完成端至端的通用协议输入,包括LVTTL/LVCMOS/LVCMOS18协议。可编程延迟模块对信号输入通路的信号进行可编程延迟,使其与D触发器的时钟信号CLK同步,最终通过选择器(MUX)选择信号为直接输入或经过延迟输入。

2 电路实现

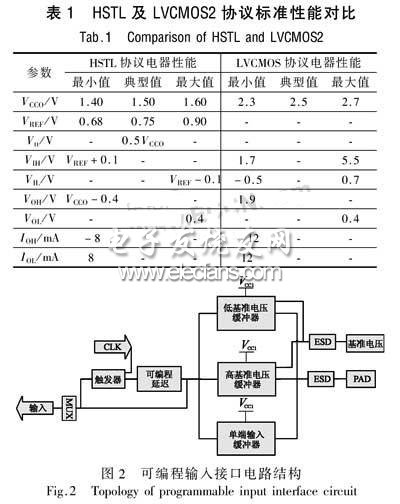

就低基准电压缓冲器而言,设计采用PMOS差分输入级。影响性能指标的关键因素包括输入差分放大器的增益、噪声容限、共模抑制能力等。输入协议中频率最高的是HSTL协议,它可以达到200 MHz以上的工作频率。以HSTL协议为例,JEDEC8标准定义了DC及AC两种逻辑标准,且两种标准之间有大约100 mV的电平差值。这是因为当输入信号始终大于DC阈值时,逻辑状态可以保持稳定,避免发生翻转,便于设计高增益的差分输入级。噪声容限NM在输入输出电路中是特别重要的指标,过低的噪声容限会容易引起逻辑错误。高噪声容限NMH与低噪声容限NML分别定义为

对于HSTL协议来说,单端输入时的典型VMH及NML均为250 mV,差分输入时则可以抑制650 mV的共模噪声,在设计时还应尽量提高差分输入管的等效小信号增益gm,提高共模抑制比CMRR。为防止衬底噪声耦合到输入通路,可以在设计时在版图中加入保护环,对其进行隔离。

高基准电压缓冲器设计思路与低基准电压缓冲器基本相同,但输入端采用的是NMOS差分输入级。单端输入缓冲器的基本结构类似于一个施密特触发器,具有较高的输入门限电压,在输入信号达到门限电压之后,输出通过缓冲器翻转,并进行整形。

可编程延迟模块采用多级反相器延迟线结构,并有多个选择输入路径,利用各个路径反相器数量及尺寸的不同,通过四个开关管控制延迟量。在进入芯片之前,经过延迟的信号与未经过延迟的信号还可通过一个多路选择器MUX进行选择,以满足内部时钟的不同需要。最终完成的电路如图3所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)