本次设计的数字频率计以AT89C52为核心,在软件编程中采用的是C51语言,测量采用了多周期同步测量法,它避免了直接测量法对精度的不足,同时消除了直接与间接相结合方法,需对被测信号的频率与中介频率的关系进行判断带来的不便,能实现较高的等精度频率和周期的测量。

硬件电路设计方案多周期同步测量法的基本思路是使被测信号与闸门之间实现同步化,从而从根本上消除了在闸门时间内对被测信号进行计数时的±1量化误差,使测量精度大大提高。倒数计数器就是基于该方法而设计出来的一种具有创新思想的测频、测周期的仪器。它采用多周期同步测量法,即测量输入多个(整数个)周期值,再进行倒数运算而求得频率。其优点是:可在整个测频范围内获得同样高的测试精度和分辨率。

1、系统级方案设计

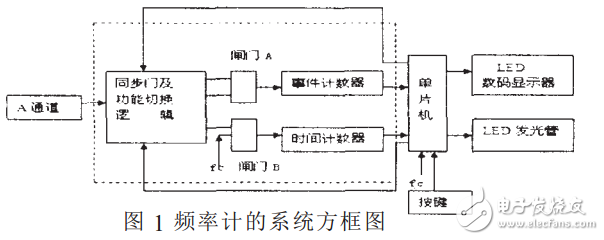

在选择多周期同步等精度测量法的情况下,按照自顶向下的设计方法,可以画出该频率计的系统级框图,如图1所示。根据测周期、频率的原理,可以将总体框图分为三个子系统:输入通道(即前置整形电路)该部分主要由模拟电路组成的;多周期同步等精度频率、周期的测量、控制及功能切换(中间部分),该部分基本上由数字硬件电路组成;单片机及外围电路,包括单片机、数码显示。

2、子系统设计

1.输入通道的设计。输入通道是由前置放大器和整形器组成的,所以要对前置放大器的增益和带宽指标进行估计。为了能准确测量信号,将输入信号经过一个放大整形电路。其具体实施方案为:将输入信号经过LM358运放放大,再通过74LS132整形,此时的信号还不能直接送入单片机,这是因为在硬件上CPU对INT0和INT1引脚的信号不能控制,解决这个问题要通过硬件,再配合软件来解决。

2.预置闸门时间发生电路设计。闸门时间的确定,可以先由一个555定时器产生一个脉冲信号,将555产生的脉冲信号送入到74LS90十进制计数器当中,由于74LS90具有二-五进制混合计数的功能,所以可以用它来实现五进制计数,将74LS90的输出接到3—8线译码器74LS138的输入端,再将译码器的输出端接上五个发光二极管,这样就可以实现硬件上的闸门时间控制。但是考虑到硬件实现上的复杂性,可以通过软件上来实现,就是将五个发光二极管直接接到单片机的P1口由软件上来实现,通过按键来改变它的闸门时间。

3.数码显示电路的设计。该部分电路是由单向八位移位寄存器74LS164和数码管组成的。考虑到精度的问题,取五位计数值,采用五片74LS164级联,同时还要显示频率和周期的单位,所以还需再级联一块74LS164,在74LS164的输出端接六个单位指示灯,分别表示周期频率的三个不同的单位数量级,即周期单位s,ms,μs和频率单位Hz,KHz及MHz。移位寄存器的时钟信号是由单片机的串行输出口TXD脚控制。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)