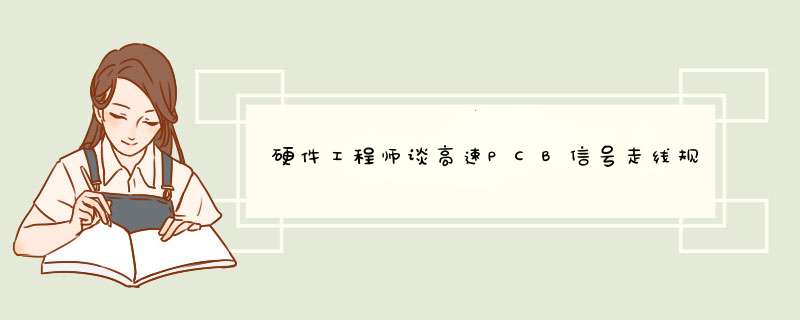

规则一:高速信号走线屏蔽规则

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

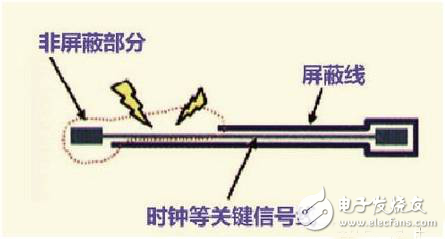

规则二:高速信号的走线闭环规则

由于PCB板的密度越来越高,很多PCB LAYOUT工程师在走线的过程中,很容易出现一种失误,即时钟信号等高速信号网络,在多层的PCB走线的时候产生了闭环的结果,这样的闭环结果将产生环形天线,增加EMI的辐射强度。

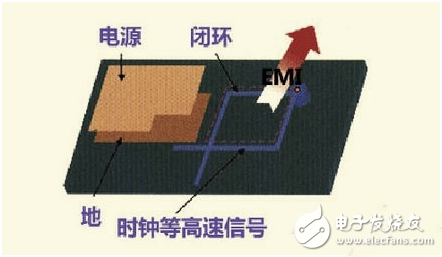

规则三:高速信号的走线开环规则

规则二提到高速信号的闭环会造成EMI辐射,然而开环同样会造成EMI辐射。

时钟信号等高速信号网络,在多层的PCB走线的时候一旦产生了开环的结果,将产生线形天线,增加EMI的辐射强度。

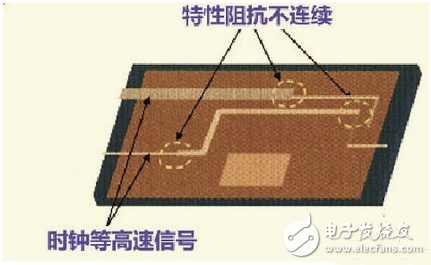

规则四:高速信号的特性阻抗连续规则

高速信号,在层与层之间切换的时候必须保证特性阻抗的连续,否则会增加EMI的辐射。也就是说,同层的布线的宽度必须连续,不同层的走线阻抗必须连续。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)