应用选择

为了说明使用高开关频率的权衡过程,我们设计了三个独立电源,其工作频率分别为100、300和750 kHz。所有这三种设计,输入电压均为48V,输出电压均为5V,而输出电流均为1A。这些要求常用于为一个5-V逻辑USB,或者为其它DC/DC转换器使用的中频通用5-V总线供电,例如:低压降稳压器等。若想建立一些设计限制,所选允许纹波电压需为50mV,其约为输出电压的1%;同时选择使用0.5 A的峰至峰电感电流。德州仪器TPS54160是一种集成MOSFET的2.5-MHz、60-V、1.5-A降压DC/DC转换器,用作所有设计的稳压器。TPS54160特有外部补偿和快速可编程频率,适用于一些高输入电压的工业应用。

电感和电容选择

根据下列四个简化公式,选择每种情况的电感和电容:

电感选择

(1a)

可重写为:

(1b)

其中,D(占空比)=5 V/48 V=0.104,且△I = 0.5 A峰至峰。

电容选择

I= C x dv/dt (2a)

可重写为:

(2b)

其中,△I = 0.5 A峰至峰,且△V=50 mV。

就方程式2b而言,我们假设所选电容的等效串联电阻(ESR)忽略不计,陶瓷电容便是如此。我们选择陶瓷电容,用于所有三种设计,原因是其低电阻和小尺寸。方程式2b分子的乘数2表明DC偏压相关电容下降情况,原因是大多数陶瓷电容的数据表中都没有说明这一效应。

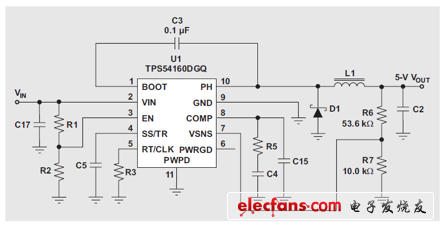

图 1 TPS54160 参考示意图

图1所示电路用于评估实验台上每种设计的性能。示意图中没有值的一些组件,为设计中修改了的组件。输出滤波器由L1和C2组成。所有三种设计的组件值都列举在表1中,这些值的选择是基于方程式1a到2b的结果。注意,每个电感的DC电阻随频率增加而减小。这是因为较少的匝数所需的铜长度更短。我们单独为每个开关频率设计了误差放大器补偿组件。选择补偿值的计算方法,超出了本文讨论的范围。

最小“导通”时间

最小可控“导通”时间限制是DC/DC转换器IC的一个特点,其为脉宽调制(PWM)电路的最窄可达脉宽。在降压转换器中,开关周期期间功率MOSFET导通的时间百分比被称作占空比,其等于输出电压与输入电压的比。使用TPS54160转换器时,占空比为0.104(4 V/48 V),而数据表中列出的最小“导通”时间为130 ns。可控脉宽限制产生一个最小可达占空比,而用最小“导通”时间乘以开关频率,我们可以轻松地计算出该占空比的大小。一旦知道了最小占空比,利用VIN乘以最小占空比,我们便可以计算出最低可达输出电压。最低输出电压同样也受转换器基准电压的限制,使用TPS54160时其为0.8V。

本例中,我们可以通过750-kHz开关频率来产生一个5-V输出电压(参见表2)。但是,如果该频率为1 MHz,则最低可能输出电压被限制为约6V;否则,DC/DC转换器会跳过脉冲。替代方法是降低输入电压或者频率。在选择某个开关频率以前,你最好是先查看DC/DC转换器数据表,了解保证最小可控“导通”时间。

脉冲跳跃

DC/DC转换器无法足够快速地清除门驱动脉冲来维持理想占空比时,便会出现脉冲跳跃。电源会尝试调节输出电压,但由于距离更远的脉冲,纹波电压会增加。由于存在脉冲跳跃,输出纹波会呈现出分谐波成分,其可能出现噪声问题。限流电路也可能不再正常工作,因为IC可能不响应大电流峰值。一些情况下,如果控制器不正常工作,控制环路便可能会不稳定。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)