TI公司的AM3359是基于高达1GHz的Sitara™ARM Cortex-A8 32位RISC处理器的工业通信引擎(ICE),具有增强的图像和图形处理,外设和工业接口选择如EtherCAT和PROFIBUS,支持高等级 *** 作系统(HLOS)。还包含NEON™ SIMD协处理器,集成了32KB L1指令和32KB数据缓存,256KB ECC L2缓存,176KB引导ROM,64KB专用RAM,仿真和调试-JTAG,多达128个中断请求的中断控制器,64KB通用片上存储器控制器(OCMC)RAM,主要用在游戏外设,家庭和工业自动化,消费类医疗设备,打印机和智能收费系统。本文介绍了AM3359主要特性,功能框图以及EtherCAT通信开发平台TIDEP0001主要特性,电路图和材料清单。

The AM335x microprocessors, based on the ARM Cortex-A8 processor, are enhanced with image,graphics processing, peripherals and industrial interface opTIons such as EtherCAT and PROFIBUS. Thedevices support high-level operaTIng systems (HLOS)。 Processor SDK Linux® and TI-RTOS are availablefree of charge from TI.

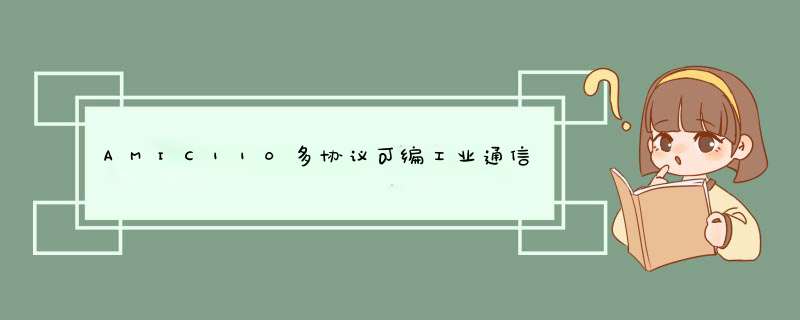

The AM335x microprocessor contains the subsystems shown in the Functional Block Diagram and a briefdescription of each follows:

The contains the subsystems shown in the Functional Block Diagram and a brief description of eachfollows:

The microprocessor unit (MPU) subsystem is based on the ARM Cortex-A8 processor and the PowerVRSGX™ Graphics Accelerator subsystem provides 3D graphics acceleration to support display and gamingeffects.

The PRU-ICSS is separate from the ARM core, allowing independent operation and clocking for greaterefficiency and flexibility. The PRU-ICSS enables additional peripheral interfaces and real-time protocolssuch as EtherCAT, PROFINET, EtherNet/IP, PROFIBUS, Ethernet Powerlink, Sercos, and others.

Additionally, the programmable nature of the PRU-ICSS, along with its access to pins, events and allsystem-on-chip (SoC) resources, provides flexibility in implementing fast, real-time responses, specializeddata handling operations, custom peripheral interfaces, and in offloading tasks from the other processorcores of SoC.

AM3359主要特性:

• Up to 1-GHz Sitara™ ARM® Cortex®-A8 32‑BitRISC Processor

– NEON™ SIMD Coprocessor

– 32KB of L1 Instruction and 32KB of Data CacheWith Single-Error Detection (Parity)

– 256KB of L2 Cache With Error Correcting Code(ECC)

– 176KB of On-Chip Boot ROM

– 64KB of Dedicated RAM

– Emulation and Debug - JTAG

– Interrupt Controller (up to 128 InterruptRequests)

• On-Chip Memory (Shared L3 RAM)

– 64KB of General-Purpose On-Chip MemoryController (OCMC) RAM

– Accessible to All Masters

– Supports Retention for Fast Wakeup

• External Memory Interfaces (EMIF)

– mDDR(LPDDR), DDR2, DDR3, DDR3LController:

– mDDR: 200-MHz Clock (400-MHz Data Rate)

– DDR2: 266-MHz Clock (532-MHz Data Rate)

– DDR3: 400-MHz Clock (800-MHz Data Rate)

– DDR3L: 400-MHz Clock (800-MHz DataRate)

– 16-Bit Data Bus

– 1GB of Total Addressable Space

– Supports One x16 or Two x8 Memory DeviceConfigurations

– General-Purpose Memory Controller (GPMC)

– Flexible 8-Bit and 16-Bit AsynchronousMemory Interface With up to Seven Chip Selects (NAND, NOR, Muxed-NOR, SRAM)

– Uses BCH Code to Support 4-, 8-, or 16-BitECC

– Uses Hamming Code to Support 1-Bit ECC

– Error Locator Module (ELM)

– Used in Conjunction With the GPMC toLocate Addresses of Data Errors fromSyndrome Polynomials Generated Using aBCH Algorithm

– Supports 4-, 8-, and 16-Bit per 512-ByteBlock Error Location Based on BCHAlgorithms

• Programmable Real-Time Unit Subsystem andIndustrial Communication Subsystem (PRU-ICSS)

– Supports Protocols such as EtherCAT®,PROFIBUS, PROFINET, EtherNet/IP™, and

More

– Two Programmable Real-Time Units (PRUs)

– 32-Bit Load/Store RISC Processor Capableof Running at 200 MHz

– 8KB of Instruction RAM With Single-ErrorDetection (Parity)

– 8KB of Data RAM With Single-Error Detection(Parity)

– Single-Cycle 32-Bit Multiplier With 64-BitAccumulator

– Enhanced GPIO Module Provides Shift-In/Out Support and Parallel Latch on External Signal

– 12KB of Shared RAM With Single-ErrorDetection (Parity)

– Three 120-Byte Register Banks Accessible byEach PRU

– Interrupt Controller (INTC) for Handling SystemInput Events

– Local Interconnect Bus for Connecting Internaland External Masters to the Resources Insidethe PRU-ICSS

– Peripherals Inside the PRU-ICSS:

– One UART Port With Flow Control Pins,Supports up to 12 Mbps

– One Enhanced Capture (eCAP) Module

– Two MII Ethernet Ports that Support IndustrialEthernet, such as EtherCAT

– One MDIO Port

• Power, Reset, and Clock Management (PRCM)Module

– Controls the Entry and Exit of Stand-By andDeep-Sleep Modes

– Responsible for Sleep Sequencing, PowerDomain Switch-Off Sequencing, Wake-Up Sequencing, and Power Domain Switch-OnSequencing

– Clocks

– Integrated 15- to 35-MHz High-FrequencyOscillator Used to Generate a Reference

Clock for Various System and PeripheralClocks

– Supports Individual Clock Enable and DisableControl for Subsystems and Peripherals toFacilitate Reduced Power Consumption

– Five ADPLLs to Generate System Clocks(MPU Subsystem, DDR Interface, USB and Peripherals [MMC and SD, UART, SPI, I2C],L3, L4, Ethernet, GFX [SGX530], LCD Pixel Clock)

– Power

– Two Nonswitchable Power Domains (Real-Time Clock [RTC], Wake-Up Logic

[WAKEUP])

– Three Switchable Power Domains (MPUSubsystem [MPU], SGX530 [GFX],

Peripherals and Infrastructure [PER])

– Implements SmartReflex™ Class 2B for CoreVoltage Scaling Based On Die Temperature,Process Variation, and Performance(Adaptive Voltage Scaling [AVS])

– Dynamic Voltage Frequency Scaling (DVFS)

• Real-Time Clock (RTC)

– Real-Time Date (Day-Month-Year-Day of Week)and Time (Hours-Minutes-Seconds) Information

– Internal 32.768-kHz Oscillator, RTC Logic and1.1-V Internal LDO

– Independent Power-on-Reset(RTC_PWRONRSTn) Input

– Dedicated Input Pin (EXT_WAKEUP) forExternal Wake Events

– Programmable Alarm Can be Used to GenerateInternal Interrupts to the PRCM (for Wakeup) orCortex-A8 (for Event Notification)

– Programmable Alarm Can be Used WithExternal Output (PMIC_POWER_EN) to Enablethe Power Management IC to Restore Non-RTCPower Domains

• Peripherals

– Up to Two USB 2.0 High-Speed DRD (Dual-Role Device) Ports With Integrated PHY

– Up to Two Industrial Gigabit Ethernet MACs (10,100, 1000 Mbps)

– Integrated Switch

– Each MAC Supports MII, RMII, RGMII, andMDIO Interfaces

– Ethernet MACs and Switch Can OperateIndependent of Other Functions

– IEEE 1588v2 Precision Time Protocol (PTP)

– Up to Two Controller-Area Network (CAN) Ports

– Supports CAN Version 2 Parts A and B

– Up to Two Multichannel Audio Serial Ports(McASPs)

– Transmit and Receive Clocks up to 50 MHz

– Up to Four Serial Data Pins per McASP PortWith Independent TX and RX Clocks

– Supports Time Division Multiplexing (TDM),Inter-IC Sound (I2S), and Similar Formats

– Supports Digital Audio Interface Transmission(SPDIF, IEC60958-1,and AES-3 Formats)

– FIFO Buffers for Transmit and Receive (256Bytes)

– Up to Six UARTs

– All UARTs Support IrDA and CIR Modes

– All UARTs Support RTS and CTS FlowControl

– UART1 Supports Full Modem Control

– Up to Two Master and Slave McSPI SerialInterfaces

– Up to Two Chip Selects

– Up to 48 MHz

– Up to Three MMC, SD, SDIO Ports

– 1-, 4- and 8-Bit MMC, SD, SDIO Modes

– MMCSD0 has Dedicated Power Rail for 1.8‑Vor 3.3-V Operation

– Up to 48-MHz Data Transfer Rate

– Supports Card Detect and Write Protect

– Complies With MMC4.3, SD, SDIO 2.0Specifications

– Up to Three I2C Master and Slave Interfaces

– Standard Mode (up to 100 kHz)

– Fast Mode (up to 400 kHz)

– 32 GPIO Pins per Bank (Multiplexed WithOther Functional Pins)

– GPIO Pins Can be Used as Interrupt Inputs(up to Two Interrupt Inputs per Bank)

– Up to Three External DMA Event Inputs that canAlso be Used as Interrupt Inputs

– Eight 32-Bit General-Purpose Timers

– DMTIMER1 is a 1-ms Timer Used forOperating System (OS) Ticks

– DMTIMER4–DMTIMER7 are Pinned Out

– One Watchdog Timer

– SGX530 3D Graphics Engine

– Tile-Based Architecture Delivering up to 20Million Polygons per Second

– Universal Scalable Shader Engine (USSE) isa Multithreaded Engine Incorporating Pixel

and Vertex Shader Functionality

– Advanced Shader Feature Set in Excess ofMicrosoft VS3.0, PS3.0, and OGL2.0

– Industry Standard API Support of Direct3DMobile, OGL-ES 1.1 and 2.0, and OpenMax

– Fine-Grained Task Switching, LoadBalancing, and Power Management

– Advanced Geometry DMA-Driven Operationfor Minimum CPU Interaction

– Programmable High-Quality Image Anti-Aliasing

– Fully Virtualized Memory Addressing for OSOperation in a Unified Memory Architecture

– LCD Controller

– Up to 24-Bit Data Output; 8 Bits per Pixel(RGB)

– Resolution up to 2048 × 2048 (WithMaximum 126-MHz Pixel Clock)

– Integrated LCD Interface Display Driver(LIDD) Controller

– Integrated Raster Controller

– Integrated DMA Engine to Pull Data from theExternal Frame Buffer Without Burdening theProcessor via Interrupts or a Firmware Timer

– 512-Word Deep Internal FIFO

– Supported Display Types:

– Character Displays - Uses LIDD Controllerto Program these Displays

– Passive Matrix LCD Displays - Uses LCDRaster Display Controller to ProvideTiming and Data for Constant GraphicsRefresh to a Passive Display

– Active Matrix LCD Displays – UsesExternal Frame Buffer Space and theInternal DMA Engine to Drive StreamingData to the Panel

– 12-Bit Successive Approximation Register(SAR) ADC

– 200K Samples per Second

– Input can be Selected from any of the EightAnalog Inputs Multiplexed Through an 8:1

Analog Switch

– Can be Configured to Operate as a 4-Wire, 5-Wire, or 8-Wire Resistive Touch Screen

Controller (TSC) Interface

– Up to Three 32-Bit eCAP Modules

– Configurable as Three Capture Inputs orThree Auxiliary PWM Outputs

– Up to Three Enhanced High-Resolution PWMModules (eHRPWMs)

– Dedicated 16-Bit Time-Base Counter WithTime and Frequency Controls

– Configurable as Six Single-Ended, Six Dual-Edge Symmetric, or Three Dual-Edge Asymmetric Outputs

– Up to Three 32-Bit Enhanced QuadratureEncoder Pulse (eQEP) Modules

• Device Identification

– Contains Electrical Fuse Farm (FuseFarm) ofWhich Some Bits are Factory Programmable

– Production ID

– Device Part Number (Unique JTAG ID)

– Device Revision (Readable by Host ARM)

• Debug Interface Support

– JTAG and cJTAG for ARM (Cortex-A8 andPRCM), PRU-ICSS Debug

– Supports Device Boundary Scan

– Supports IEEE 1500

• DMA

– On-Chip Enhanced DMA Controller (EDMA) hasThree Third-Party Transfer Controllers (TPTCs)and One Third-Party Channel Controller(TPCC), Which Supports up to 64

Programmable Logical Channels and EightQDMA Channels. EDMA is Used for:

– Transfers to and from On-Chip Memories

– Transfers to and from External Storage(EMIF, GPMC, Slave Peripherals)

• Inter-Processor Communication (IPC)

– Integrates Hardware-Based Mailbox for IPC andSpinlock for Process Synchronization BetweenCortex-A8, PRCM, and PRU-ICSS

– Mailbox Registers that Generate Interrupts

– Four Initiators (Cortex-A8, PRCM, PRU0,PRU1)

– Spinlock has 128 Software-Assigned LockRegisters

• Security

– Crypto Hardware Accelerators (AES, SHA,RNG)

– Secure Boot

• Boot Modes

– Boot Mode is Selected Through Boot

Configuration Pins Latched on the Rising Edgeof the PWRONRSTn Reset Input Pin

• Packages:

– 298-Pin S-PBGA-N298 Via Channel Package(ZCE Suffix), 0.65-mm Ball Pitch

– 324-Pin S-PBGA-N324 Package(ZCZ Suffix), 0.80-mm Ball Pitch

AM3359应用:

• Gaming Peripherals

• Home and Industrial Automation

• Consumer Medical Appliances

• Printers

• Smart Toll Systems

• Connected Vending Machines

• Weighing Scales

• Educational Consoles

• Advanced Toys

图1.AM335x系列MPU功能框图

EtherCAT通信开发平台TIDEP0001

Targeted for EtherCAT slave communications, this development platform allows designers to implement real-time EtherCAT communications standards in a broad range of industrial automation equipment. It enables low foot print designs in applications such as industrial automation, factory automation or industrial communication with minimal external components and with best in class low power performance. Although this TI Design was done on the TMDSICE3359, it can also be done on the TMDXICE110.

EtherCAT通信开发平台TIDEP0001主要特性:

EtherCAT conformance tested by EtherCAT Technology Group (ETG)

Free EtherCAT Slave Stack Code (SSC) from Beckhoff available; requires ETG membership (free of charge) and valid EtherCAT Vendor ID.

Free board support package and industrial software development kit from TI

Support other industrial communications with the same hardware (e.g., PROFIBUS, Profinet, Ethernet/IP and more)

Production Ready development platform sub-system which includes schematics, BOM, user guides, application notes, white paper, software, demos and more

图2.EtherCAT通信开发平台TIDEP0001外形图

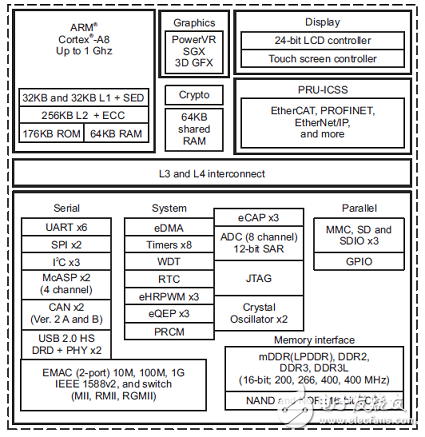

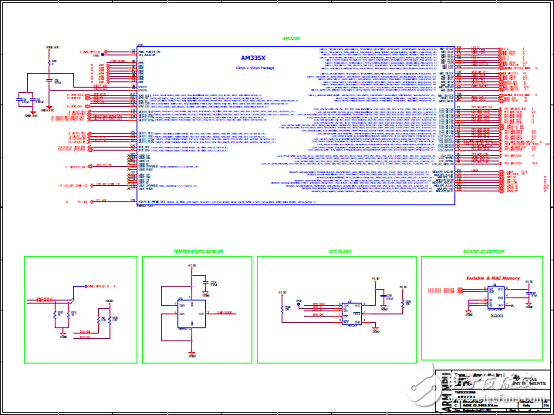

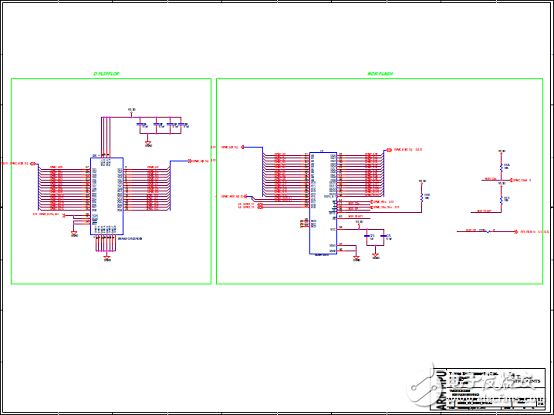

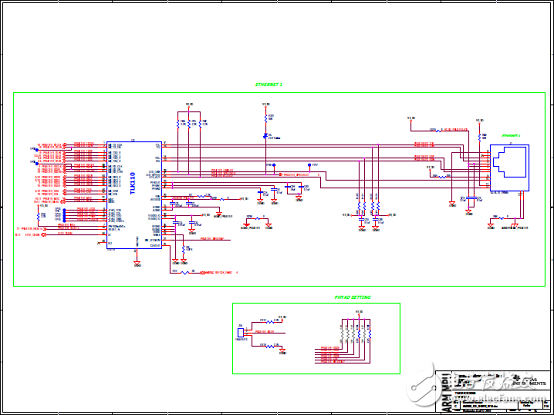

图3. EtherCAT通信开发平台TIDEP0001电路图(1)

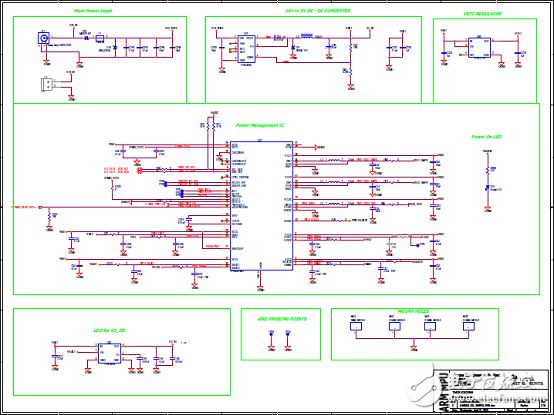

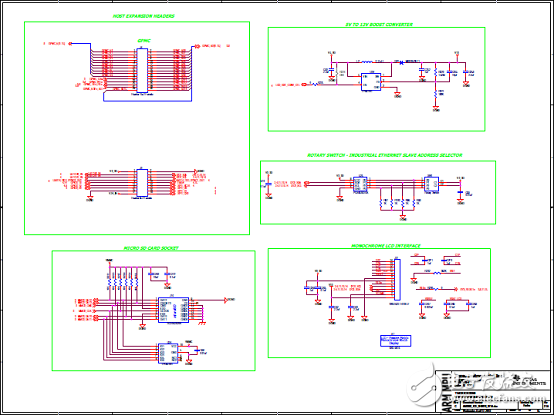

图4. EtherCAT通信开发平台TIDEP0001电路图(2)

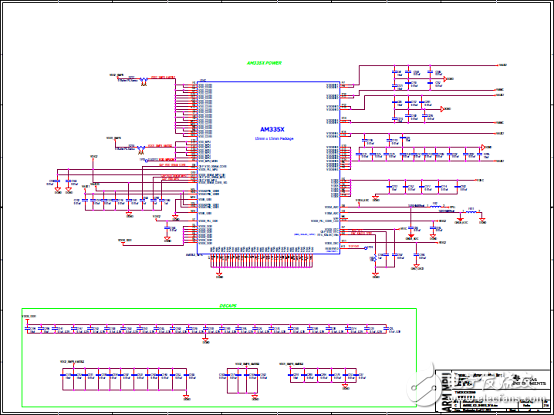

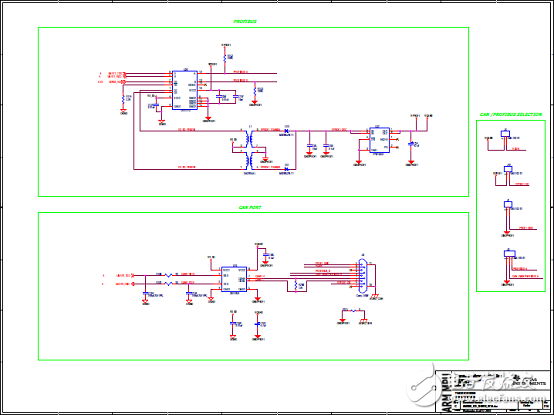

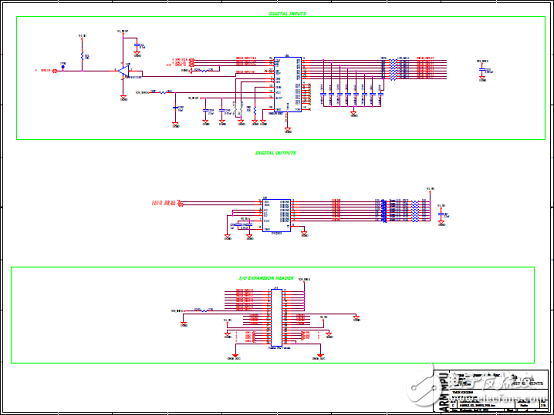

图5. EtherCAT通信开发平台TIDEP0001电路图(3)

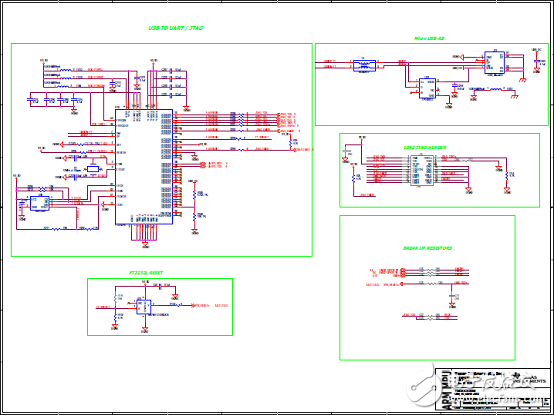

图6. EtherCAT通信开发平台TIDEP0001电路图(4)

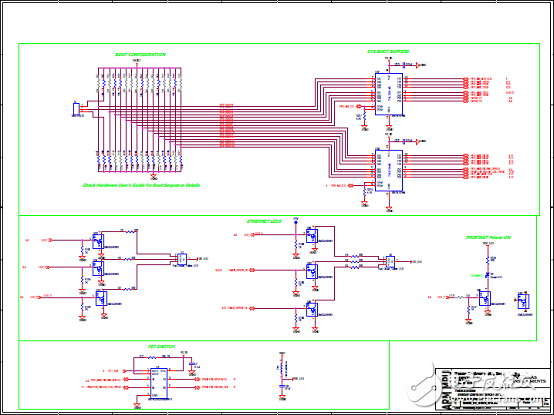

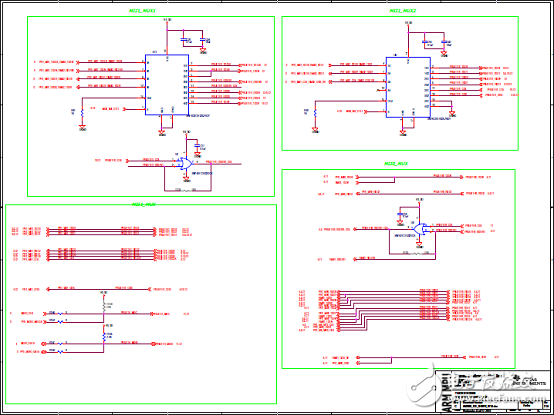

图7. EtherCAT通信开发平台TIDEP0001电路图(5)

图8. EtherCAT通信开发平台TIDEP0001电路图(6)

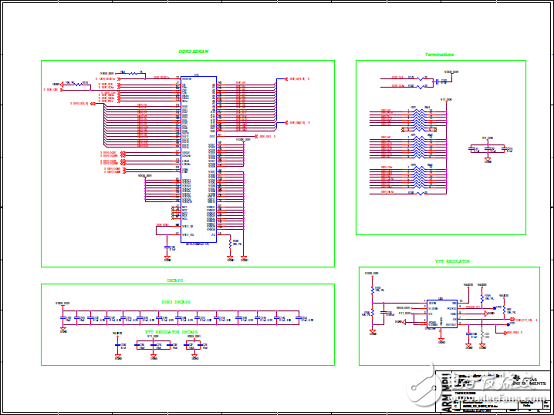

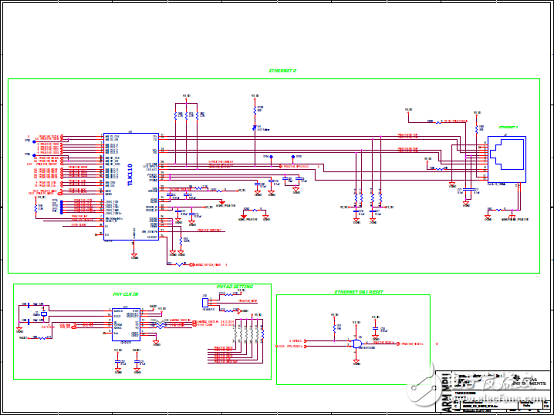

图9. EtherCAT通信开发平台TIDEP0001电路图(7)

图10. EtherCAT通信开发平台TIDEP0001电路图(8)

图11. EtherCAT通信开发平台TIDEP0001电路图(9)

图12. EtherCAT通信开发平台TIDEP0001电路图(10)

图13. EtherCAT通信开发平台TIDEP0001电路图(11)

图14. EtherCAT通信开发平台TIDEP0001电路图(12)

图15. EtherCAT通信开发平台TIDEP0001电路图(13)

图16. EtherCAT通信开发平台TIDEP0001电路图(14)

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)