从现状看来,随着封装业者开始逐步转入2.5D/3D技术,高密度Fan-out和其他封装工艺,可见的先进IC封装市场似乎开始进入了一个高风险的竞争战场。

而回顾整个封装技术的变革,在TSMC在几年前开始涉足先进封装技术之后,曾经一度由OSAT主导并掌控的客户芯片封装需求的市场逐渐发生了变化,今年苹果的A10封装导入了台积电的的Fan-out技术,对OSAT来说就是一个信号。

而在这之后,也传出了三星和Intel将谋划进攻先进封装产业,如果真是这样的话,那么第一阵型的三个Fab将会在不久的将来直接和OSAT竞争,虽然并不是所有的Fab都有这样的能力,但Fab第一梯队的进入,会对OSAT造成冲击。

同时根据分析机构披露,在A10的Fan-out封装上尝到甜头的台积电在先进封装上加大了研发和投资的力度。他们用在先进封装研发上的资金已高达10亿美元。而Intel也表示,他们在先进封装上的研发成本比两个最大的OSAT加起来的研发成本还要高。一场Fab和OSAT的奇怪战争,即将打响。

作为回应,OSAT掀起了并购热潮,准备通过整合资源的方式来应对这种挑战。日月光和矽品的合并就是明显的一个例子。

但据观察,这股趋势也会给他们的芯片设计客户带来新的困扰:

首先就是芯片制造商和OEM们正在评估这些封装技术,为其未来的产品选择合适的方案,但这看起来是一个很复杂和困难的工作;

其次,为了寻找一个先进封装的供应商,现在他们又面临了三种选择:Fab的整体解决方案、OSAT单独解决、Fab和OSAT联手解决封装。

对于这些芯片厂商和OEM来说,如何选择解决办法,就成为了一个大问题。

但就我们看来,因为每周解决方法都有相应的有点和决定,所以最终选择哪种封装解决方案,是由需求决定的。

例如,如果选择Fab一站式解决制造和封装的这种方案,由于整个流程由Fab *** 控,因此中间很多的花费就由Fab主导,芯片制造商们议价的能力就不高,丧失了以前了OSAT谈判的灵活性。当然这些选择跟多取决于客户需求。

虽然目前有很多厂商投入到Fan-out等技术的研发,也有很多的潜在OSAT兼并事件将发生,但是从目前看来,我们也不能那种封装技术会在未来中胜出,OSAT产业面临大问题了。

先进封装前景看好

Fab和OSAT都在追逐先进封装技术,归根到底就一个字——钱。因为根据很多分析机构的报告,先进封装在未来会是一个大市场。因此Fab想在萧条的IC工业中寻找新的成长空间,就瞄向了先进封装;而这本身就是OSAT挣钱的来源,努力巩固已有市场也是刻不容缓。

根据数据显示,到2020年,先进封装的市场规模预计会高达300亿美元,较之2014年的202亿美元有显著的增长。倒装芯片会长期在这个市场中扮演一个重要角色。但在可预见的未来,Fan-out的成长速度会非常快。

根据Yole的数据,到2020年,Fan-out的市场规模会从2015年的2.44亿美元暴增到24亿美元。

与此同时,使用TSV的2.5D封装技术在未来几年的年成长率也会高达22%。

而据观察,推动先进封装往快速增长的原因有以下几点,最明显的就是芯片制造商想缩小封装尺寸,并提高芯片性能。在芯片的制造过程中,有很多因素需要考虑,但由于封装对于整体成本和性能有重要的影响,所以一般芯片制造商在早期就会在选择的时候非常慎重,这就是是先进封装发展的动力之一。

举个例如,在过去,智能手机芯片用的最多的封装技术是POP封装,虽然这个技术还是被手机芯片采用,但很显然的是,它不再是主流。因为厚度0.5左右的POP芯片在带宽和能耗上面的一些限制逐渐凸显。而为了取替POP,晶圆厂和OSAT投入到了一系列先进和具有竞争性的技术的研发。

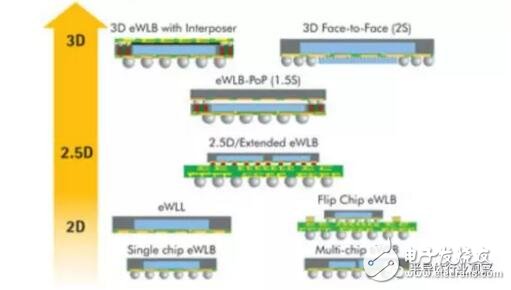

当中一个出色竞争者就是应用在苹果A10上的扇出型晶圆级封装技术(FOWLP),晶圆级封装是指在芯片还是Wafer阶段就引入封装流程,这样就可以缩小封装尺寸。

而在Fan0-out,独立的die嵌入到环氧材料中,而内部连接则在RDL到焊接凸点之间扇形展开,这样则可以实现更多的I/O。

从低pin的应用到高pin的FPGA,Fan-out对于芯片设计商的吸引力都是巨大的。

另外,多芯片解决方案也会逐渐受关注,这种根据需要,将其SoC上不同Fab技术的数字和模拟部分分割开的方法能获得更好的解决方案。

而对客户来说,Fan-out能给他们提供更多的选择。

例如在降低SoC设计的尺寸上,相较于使用传统的方式,Fan-out能更好的实现高集成度的系统级封装,随着NRE成本的增加,这是一个很好的选择。更重要的是,Fan-out能够满足即将爆发的IoT多样化应用的需求。

但我们也不能否认,客户也面临着选择的烦恼。就拿高密度的Fan-out来说,就有三种不同的方案:chip-first/face-down; chip-first/face-up和chip-last(RDL first)。

Chip-first是在生成RDL之前,先将die附着在一个临时或者永久的材料架构上的工艺进程、而Chip-last则是先生成RDL,再导入die的过程。

第一波Fan-out潮流叫eWLB(embedded wafer-level ball-grid array),那时候采用的是chip-first/face-down方案。

现在,ASE、JCET/STATS,、Namium和其他厂商正在追逐第二波Fan-out封装技术,他们追逐的也是一种接近于eWLB的chip-first/face down技术。这对于小die尺寸、低I/O和不多的RDL来说,是一个完美的选择。

与此同时,TSMC和Deca则选择Chip-first/face up的方案,这样能够支持更多的I/O,更多的RDL层,更小的线宽。

而Amkor则在追逐chip-down方案。这种方案对于那些将memory和其它die结合在一起的AP来说,是一个很好的选择。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)