4G无线通信涵盖的频段众多,且须向后兼容3G/2G技术,造成网络设备与终端用户装置极大的设计挑战,因此相关产品开发商已开始利用软件定义无线电(SDR)技术简化硬件配置,并提高支持各种无线电频段的d性,以加快多频多模产品开发时程。

由于行动装置的普及,终端消费者往往身上同时配备多台行动装置,而这些也都成为现代人必备的生活必需品。这些装置的增加,亦造就用户对于通讯流量的需求不断的往大流量与大带宽增加,因而无线网络通讯也就由2G延续到3G,再往今日的4G延伸,而未来的5G规画也在各国间展开。

经由如此的脉络轨迹,可以发现面对不同的网络速度需求,提供服务的网络设备亦须不断的发展及更新,且最近几年的数据需求量爆炸性的成长,亦使设备开发工程师面临时程紧缩的压力。另一方面,对于提供通讯服务的营运商来说,快速的网络基础建置速度等同于大量的使用者加入,亦等同于良好的使用者经验及利润。

早在1990年代中期,北美地区就已开始发展软件定义无线电(SDR),当时着重在2G的空中接口(Air Interface),但是受限于技术因素,使用者端设备采取SDR开发的商业模式并不成功,因此将SDR应用在3G基地台设备上,也就成为此技术的发展方向,如此延续到4G基地台的开发上更加被重视。

传统上,建构一个无线电系统并非易事,它的设计大部分采用模拟电路与组件,比如天线、振荡器、滤波器、讯号放大器、讯号调变及解调变器、多任务/解多任务器等。此外,采用模拟组件的设计不仅造成售价昂贵,制造成本亦无法压低,往往也需要工程师不断的调整与测试,才能达到良好的运作方式。如此设计出来的无线系统,并无法提供设备在成品完成后的性能可调整或重组(Reconfigurable)能力,造成一旦有须要修改或是系统内部更新时,就必须重新设计与制造,此为影响设计成本最大的原因。

SDR的出现,是希望提供一个可调整或重组能力的无线电硬件解决方案,并利用软件来加以设定及配置,即可因应不同的使用需求、不同的无线电频段,提供不同的网络带宽、不同的无线装置所需的讯号调变及解调变功能等需求。

Joseph Mitola III教授于1992年所提出的软件无线电概念,也希望最终能够达到在软件无线电的系统架构里面的设备与系统,在不脱机情况下,能够达成动态的调整与设定此系统上无线电讯号的处理模块与各种参数,以因应不同的需求。在目前长程演进计划(LTE)的基地台开发阶段上,同样希望以能够可调整或重组能力的组件,加速设备的开发时程,提高营运商的布建d性。

SDR射频前端日新月异自从SDR的想法被提出,相关的功能与运用就被不断地开发出来,众多厂商的产品都宣称具备SDR功能,这里就介绍主要的功能区块。

小型基地台(Small Cell)射频前端的SDR可以分为两个大架构,一个模拟射频讯号的模块,与一个基频讯号处理的区块。目前有许多的厂家推出各自的SDR模块设计,并提供一个测试环境给工程师快速的参考使用,增加自家芯片的市场占有率,同时也会推广到开放硬件与软件论坛,让更多人可以实际的测试使用,而这些公开的信息也能够用来了解SDR的设计架构,以及Small Cell应用上的情况。

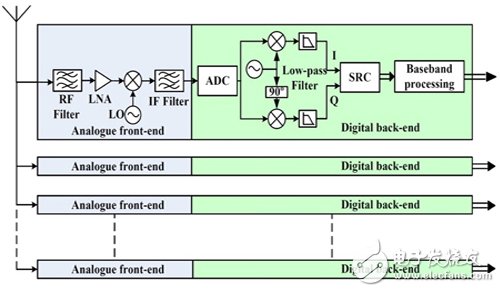

由于射频前端的无线电模块集成电路不断演进,早期分离式组件组成的射频收发器讯号电路,于2000年后已有模块化的方案出现,可以提供制造输出低功率的小型无线电设备厂商使用。此时模拟组件,如模拟/数字信号转换器与讯号调变及解调变器、还有多任务/解多任务器等都已整合模块化,使得用于制作前端射频模块的线路复杂度降低许多。但是要制作多频多模的产品时,设备商使用的仍然是硬件定义无线电(HDR)(图1),利用多层的硬件线路来达成多频多模的系统需求。

图1 多频多模硬件定义无线电

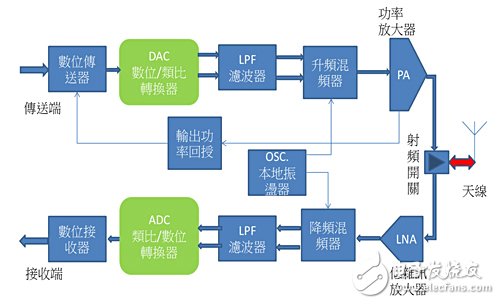

小型基地台开发商制作多频多模产品时,若采用分离式射频收发器讯号链模块化方案的电路(图2),制作上仍然会导致产品设计时间冗长,且垫高生产成本。所以就有厂商开发出整合型射频收发器,期望能协助开发厂商简化产品设计,并缩减整体物料清单(BOM)成本。

图2 分离式组件组成的射频收发器区块

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)