本文分析了高性能肖特基势垒二极管和 D 型 HEMT 在基于 p-GaN HEMT 的 200-V GaN-on-SOI 智能功率 IC 平台上的成功协同集成。这些组件的添加使芯片设计具有扩展的功能和更高的性能,使单片集成 GaN 功率 IC 更进一步。这一成就为更小、更高效的DC/DC 转换器和 PoL 转换器 铺平了道路。

GaN:电力电子领域的硅解决方案

几十年来,基于硅的功率晶体管(如 MOSFET)构成了功率转换系统的主干,可将交流电 (AC) 转换为直流电 (DC),反之亦然,或者将直流电从低压转换为高压,反之亦然。在寻求可以提高开关速度的替代品时,氮化镓迅速成为领先的候选材料之一。GaN/AlGaN 材料体系表现出更高的电子迁移率和更高的击穿临界电场。结合高电子迁移率晶体管 (HEMT) 架构,与同类硅解决方案相比,它使器件和 IC 具有更高的击穿强度、更快的开关速度、更低的电导损耗和更小的占位面积。

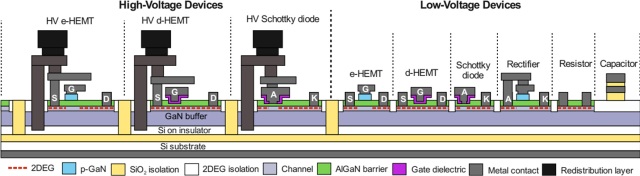

imec 的 200-V GaN-on-SOI 功率 IC 技术和组件的横截面示意图。该工艺采用 E-/D-mode HEMT、肖特基二极管、电阻器和电容器的单片共集成,并包括先进的工艺模块(深沟隔离、衬底接触、再分布层等)。

今天,大多数 GaN 电源系统由多个芯片组成。基于 GaN 的器件在组装到印刷电路板上之前作为分立元件组装。这种方法的缺点是存在影响器件性能的寄生电感。

Take a driver, for example. Discrete transistors with drivers on a separate chip suffer a lot from parasiTIc inductances between the output stages of the driver and the input of the transistor and in the switching node of half-bridges. GaN HEMTs have very high switching speed, which leads to ringing — an unwanted oscillaTIon of the signal — when the parasiTIc inductance is not suppressed. The best way to reduce the parasiTIcs and exploit the superior switching speed of GaN is to integrate both driver and HEMT on the same chip.

At the same time, it reduces the dead-time control between two transistors in a half-bridge, wherein one transistor has to switch off just as the other one switches on. During the time in between, there is a short-circuit between the power source and the ground, or dead time. Integrating all components on-chip will address the ringing, reduce dead time, and ultimately improve the power efficiency of your converter.

Co-integration of D-Mode HEMTs

Imec has already made tremendous progress monolithically integrating building blocks on a silicon-on-insulator (SOI) substrate such as drivers, half-bridges, and control/protection circuits. Now, researchers have succeeded in adding two sought-after components to the portfolio: depletion-mode (D-mode) HEMTs and Schottky diodes.

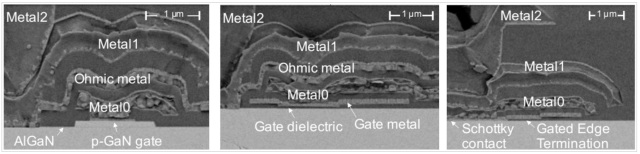

Process cross-sections of the high-voltage components fabricated on 200-mm GaN-on-SOI substrates:

(a) E-mode p-GaN HEMT; (b) D-mode MIS HEMT; (c) Schottky barrier diode. All devices include metal field plates based

on front-end and interconnect metal layers and separated by dielectric layers.

提高 GaN 功率 IC 的全部性能的主要障碍之一是找到合适的解决方案,以解决 GaN 中缺乏具有可接受性能的 p 沟道器件的问题。CMOS 技术使用互补且更对称的 p 型和 n 型 FET 对,基于两种 FET 的空穴和电子迁移率。然而,在 GaN 中,空穴的迁移率比电子的迁移率差大约 60 倍;在硅中,这只有 2 倍。这意味着以空穴为主要载流子的 p 沟道器件将比 n 沟道对应器件大 60 倍,而且效率极低。一种广泛使用的替代方法是用电阻器代替 P-MOS。电阻晶体管逻辑 (RTL) 已用于 GaN IC,但在开关时间和功耗之间表现出权衡。

Imec 通过在其 SOI 上的功能增强模式 (E-mode) HEMT 平台上共同集成 D 模式 HEMTS,提高了 GaN IC 的性能。增强和耗尽模式是指在零源电压下的开启(D 模式)或关闭(E 模式)状态,导致晶体管中有电流流动(或不流动)。Imec 预计从 RTL 到直接耦合 FET 逻辑的步骤将提高速度并降低电路的功耗。

具有低泄漏电流的肖特基二极管

肖特基势垒二极管的集成进一步提高了 GaN 功率 IC 的功率效率。与硅二极管相比,它们可以在相同的导通电阻下承受更高的电压或在相同的击穿电压下承受更低的导通电阻。

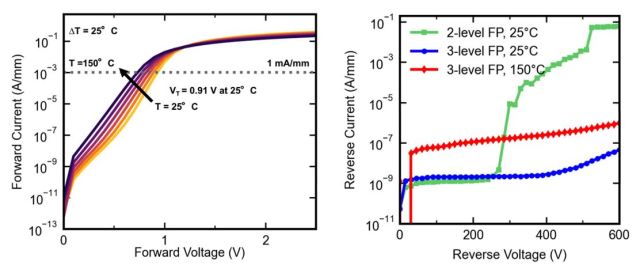

制造肖特基势垒二极管的挑战是获得低导通电压,同时获得低泄漏水平。不幸的是,当您瞄准较低的导通电压时,您最终会遇到一个小的屏障来阻止泄漏电流,而肖特基二极管因泄漏电流高而臭名昭著。与传统 GaN 肖特基势垒相比,Imec 专有的栅极边缘端接肖特基势垒二极管架构 (GET-SBD) 可实现约 0.8 V 的低开启电压,同时将漏电流降低几个数量级二极管。

制造的 GET-SBD 的特性显示(左)在 25˚C 下以半对数刻度显示 0.91 V 的低开启电压和

(右)两个不同阳极场的低反向漏电流(25˚C 时为 2 nA/mm)在

25˚C 和 150˚C下评估的板配置。

快速开关和高电压

GaN 是大功率应用的首选材料,因为引起晶体管击穿的临界电压(击穿电压)比硅高 10 倍。但由于其卓越的开关速度,GaN 在低功率应用中仍然比硅具有优势。

imec 创建的基于 GaN 的 IC 为更小、更高效的 DC/DC 转换器和负载点 (PoL) 转换器开辟了道路。例如,智能手机、平板电脑或笔记本电脑包含在不同电压下工作的芯片,需要 AC/DC 转换器为电池充电,设备内部需要 PoL 转换器以产生不同的电压。这些组件不仅包括开关,还包括变压器、电容器和电感器。晶体管的开关速度越快,这些组件就会变得越小,最终在相同功率下产生更紧凑和低成本的系统。

快速电池充电器构成了当今 GaN 的最大市场,其次是用于服务器、汽车行业和可再生能源的电源。预计使用 GaN 的电源在系统级更可靠。它们的外形尺寸和重量更小,从而减少了材料清单,从而降低了成本。

正在研究的垂直设备

Imec 将专注于提高现有平台的性能并进行进一步的可靠性测试。该公司目前提供用于原型设计的 200-V 和 650-V 平台,不久之后将推出 100V。对于具有集成组件的 GaN IC,1,200-V 大功率平台可能不会产生显着改进。电压越高,组件变得越慢。因此,可能没有必要在芯片上集成驱动程序;模拟将证实这一点。

Imec 还在寻找分立 1,200-V 器件的替代品,为电动汽车等最高电压电源应用启用 GaN 技术。具有横向拓扑的晶体管是当今占主导地位的 GaN 器件架构。这些器件的三个端子(源极、栅极和漏极)位于同一平面的表面,因此电场是横向的,跨越 GaN 缓冲层和部分后端(金属化、氧化物)。在垂直器件中,源极和栅极位于表面,而漏极位于外延叠层的底部。在这种情况下,电场流过整个堆栈。决定器件击穿电压的是源漏分离,较大的分离可以保护通道不被击穿。然而,横向放置的源极和漏极之间的距离越大,器件越大。由于用于 1,200 V 设备的芯片会变得太大,因此通常建议横向架构最高达到 650 V。相反,对于垂直器件,使用更高的电压归结为创建更厚的外延堆叠,因为源极和漏极位于堆叠的不同端。芯片的表面积不会增加。

审核编辑:刘清

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)