PS2协议读键盘值相当简单嘛,比模拟SPI、I2C简单多了...下面介绍一下具体过程.

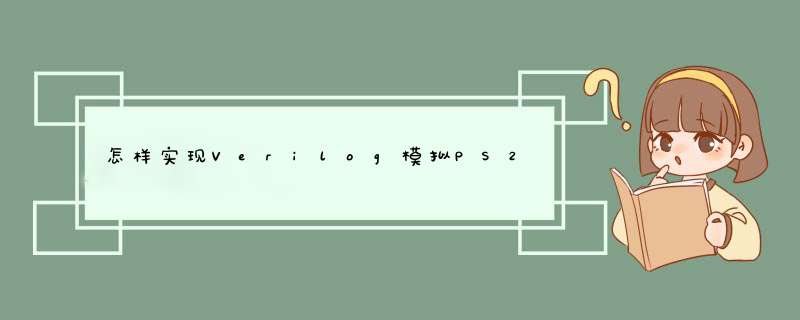

1.明确接线关系,只需接4根线,VCC要+5V,3.3我测试过不能用,时钟和数据线要用bidir双向口线,FPGA可以不用外接上拉电阻。另外,USB键盘也可以用,只要用一个转接头转成PS2即可。

2.读取基本的键盘数据,不需要FPGA发送任何数据,只需读取键盘发回来的数据即可

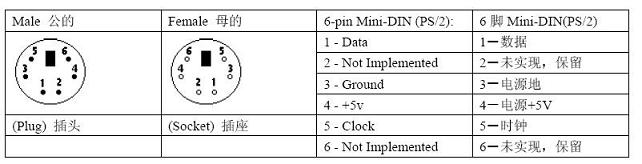

如下面的时序图,每次键盘发送11个clock信号,我们需要做的事情就是在时钟的下降沿读取数据

3.如何来采样CLK低电平?

这里可以用一个FIFO来储存数据,如下面的程序,当ps2_clk信号处于下降沿时,ps2_clk_fallingedge值将被置高

reg [2:0] ps2_clkr;//用一个fifo来采样ps2_clk信号;

always @(posedge clk)

ps2_clkr <= {ps2_clkr[1:0], ps2_clk};

wire ps2_clk_risingedge = (ps2_clkr[2:1]==2'b01); // now we can detect ps2_clk rising edges

wire ps2_clk_fallingedge = (ps2_clkr[2:1]==2'b10); // and falling edges

4.当检测到第一个低电平时,我们只需要连续读取11个周期值就可以了,这里用一个变量i来控制

always @(posedge clk)

if(rst)

i <= 0;

else

begin

if(ps2_clk_fallingedge)

begin

data2[i] <= data[i];

data[i] <= ps2_data;

if(i<10) i <= i+1;

else i <= 0;

end

end

最后来解释下这11个数据的功能,如下表

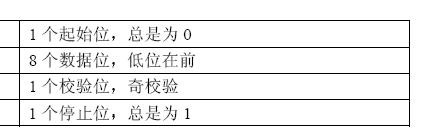

5.如果想进一步区分键值,就需要查表了,如下表

基本按键,键盘会发送“F0”+“键码”

扩展按键,则发送“E0”+“F0”+“键码”

大家都来试一下吧,一个下午就能搞定!

附程序,晶振频率降至1MHz,用LED输出键值

//==============================================================

module ps2(clk, rst, ps2_clk, ps2_data, data ,data2);

input clk, rst, ps2_clk , ps2_data;

output [10:0] data;

output [10:0] data2;

reg [3:0] i;

reg [10:0] data;//another fifo

reg [10:0] data2;

reg [2:0] ps2_clkr;//用一个fifo来采样ps2_clk信号;

always @(posedge clk)

ps2_clkr <= {ps2_clkr[1:0], ps2_clk};

wire ps2_clk_risingedge = (ps2_clkr[2:1]==2'b01); // now we can detect ps2_clk rising edges

wire ps2_clk_fallingedge = (ps2_clkr[2:1]==2'b10); // and falling edges

always @(posedge clk)

if(rst)

i <= 0;

else

begin

if(ps2_clk_fallingedge)

begin

data2[i] <= data[i];

data[i] <= ps2_data;

if(i<10) i <= i+1;

else i <= 0;

end

end

endmodule

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)