1 引言

目前,市面上主流的视频监控设备,大致可以分成两类,一是基于通用微处理器,二是基于数字信号处理器DSP。两种芯片在功能上有各自的特点,通用芯片适用于系统控制、管理和信息通讯等,DSP芯片则更适合执行复杂的数字计算、音视频数据处理等。若两种芯片协同工作,就能一定程度上克服各自的不足,更好的发挥他们的优势。基于这个考虑,本文提出了一个通用微处理器(ARM)与DSP的接口设计方案,以实现两者的实时通信。

2 系统概述

2.1 ARM7 S3C44B0X的特点

S3C44B0X是SAMSUNG公司推出的一款16/32位的RISC(Reduced InstrucTIon Set Computer)构架的处理器,它采用的是ARM7TDMI内核,最高工作频率可以达到66MHz。这是一款高性能、低功耗的微处理器,内部集成了丰富的资源,包括:8KB的Cache、RAM、LCD控制器、DMA、UART和IIC总线接口等。主要用于GPS定位系统、无线通信、手持设备、监控系统和车载装置的开发。

S3C44B0X的存储系统支持256MB的空间,划分成各32MB的8部分。系统存储器分配为BANK0~BANK7。可以分别用作外部存储器和LCD、USB等外设的连接。其中,Bank0接FLASH,用于存放系统BIOS。Bank1接FLASH硬盘,用作系统硬盘,构建文件系统。Bank2接USB口,Bank3接LCD模块,Bank6接SDRAM,Bank4、Bank5、Bank7保留。

2.2 DSP TMS20DM642的特点

TMS320DM642(简称DM642)是TMS320C6000系列中性能最好的一款定点DSP,基于美国德州仪器公司开发的Veloci TI第二代高性能超长指令字VLIW(Very Long InstrucTIon Word)构架而设计,芯片采用两级缓存的结构,能够支持一系列功能强大的外设。DM642拥有大量片上资源:64-bit 外部存储器接口、加强型DMA控制器、16/32位HPI接口、IIC总线、GPIO、多媒体卡控制器、USB、多通道音频接口、10/100Mbs以太网、管理数据输入输出模块等,是一款性能优越的多媒体处理器,是设计数字音视频处理系统的首选。

2.3主机接口HPI介绍

HPI(Host-Post InteRFace)接口是DSP与主机相连接的一个并行通信口,是构建主从式系统,实现主机与从机通信的重要接口。主机通过HPI可以访问DSP内全部的存储空间及地址空间映射的外设,进而控制DSP,实现数据交换。DM642的HPI接口有HPI16和HPI32两种工作方式,在HPI16的方式下,高16位数据端口HD[31:16]还可又用于PCI接口通信。

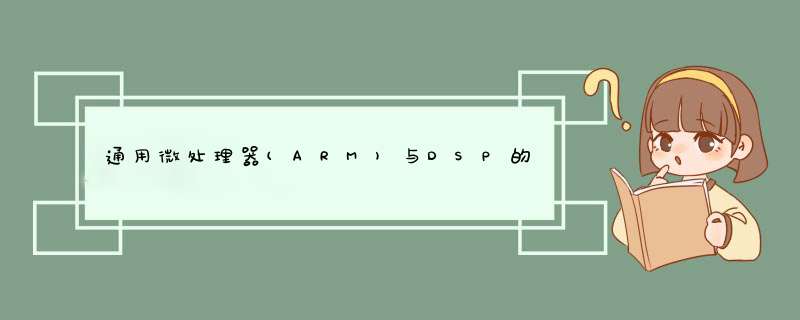

DM642的HPI接口信号线有:32条主机数据总线,在非复用模式下,数据总线只传输数据信号,而在复用模式下,还可用于地址信号的传输;HR/W_(_表示负逻辑有效)是HPI接口的读/写信号使能;HCS_、HDS1_、HDS2_是片选信号,三者在DSP的内部,经过一个逻辑门,作为数据的读/写控制逻辑;HRDY_是就绪信号,当输出为低电平,表示接口忙,反之,表示可以对接口进行 *** 作;通过控制HRDY_,可以实现主机与DSP的握手通信;HINT_为DSP对主机的中断请求输出;HHWL用于在16位模式下识别高低半字;HAS_是地址选通信号;HCNTL0/1是HPI接口的功能选择位,HCNTL0/1的功能描述如表1。

表1 HCNTL0/1功能描述

HPI寄存器共占用了256KB的内存空间,对应的16进制地址范围是:0X01880000~0X018BFFFF。其中,HPIC的起始地址为0X01880000,HPIA写的起始地址0X01880004,HPIA读的起始地址为0X01880008,其他地址空间保留。在CPU对HPI进行读写 *** 作时,必须正确的设置HPI寄存器。

3 接口设计

3.1 HPI接口读/写时序

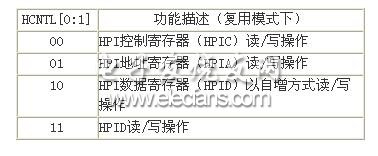

读/写时序是实现计算机 *** 作的重要一点,如果 *** 作时序不相符,就会导致读/写数据出错,甚至是 *** 作失败。所以,满足 *** 作时序是实现计算机 *** 作的先决条件之一。DM642的HPI接口 *** 作时间为1.3ns~12ns或大约5个CPU时钟脉冲。S3C44B0X的最高时钟频率可达66MHz(约为15.2ns),由此可知DM642的HPI与S3C44B0X在读/写时序上的满足要求,接口通信可以实现。DM642的HPI32读/写时序如图1,设计接口时,必须遵守该时序。由时序图可知,控制HPI的读/写时序,通过控制HCNTL、HR/W_ 、HSTROBE_、HCS_以及HRDY_这几个信号端口就能实现。

图1 HPI32的读/写时序图

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)